République Algérienne Démocratique et Populaire

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Centre universitaire Nour Bachir El Bayadh

Institut des Sciences

المركز الجامعي نور البشير البيض

معهد العلوم

**Extrait Procès-verbal

de la réunion du Conseil Scientifique

de l'Institut des Sciences du 11 Octobre 2021**

Réf : PV N°.02/CSI/2021

**POLYCOPIES EXPERTISES**

Le CSI a pris note de l'avis favorable de la part des experts désignés par ce même CSI (voir Procès-verbal du CSI du 09/03/2021), pour l'expertise du polycopié de cours déposé par les Dr BERBER Mohamed, Dr GUETTAF Yacine et Dr BENDELHOUUM Mohammed Sofiane.

**Intitulé du manuscrit :** " *FPGA et VHDL* " .

**Nombre de page du manuscrit :** 143 pages.

Le Président du CSI

Pr. Hamid Azzedine

Le Directeur de l'Institut

Dr ALAMI Omar

REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Centre Universitaire Nour Bachir El Bayadh

Institut des Sciences

Département de Technologie

Polycopié

Cours UEF 1.1.1 intitulé :

---

**INTITULE DU MODULE :**

**ELECTRONIQUE NUMERIQUE AVANCEE : FPGA ET VHDL**

---

Dr. BERBER Mohamed

**Maître de Conférences Classe « A »**

Centre Universitaire Nour Bachir – El Bayadh

Dr. GUETTAF Yacine

**Maître de Conférences Classe « A »**

Centre Universitaire Nour Bachir – El Bayadh

Dr. BENDELHOUM Mohamed Sofiane

**Maître de Conférences Classe « B »**

Centre Universitaire Nour Bachir – El Bayadh

|                                                                          |    |

|--------------------------------------------------------------------------|----|

| Liste des figures : .....                                                | 1  |

| Liste des tableaux : .....                                               | 4  |

| Introduction : .....                                                     | 5  |

| Chapitre 1 : Les Réseaux Logiques Programmables (PLD).....               | 6  |

| 1.1    Introduction .....                                                | 7  |

| 1.2    Structure de base d'un PLD :.....                                 | 8  |

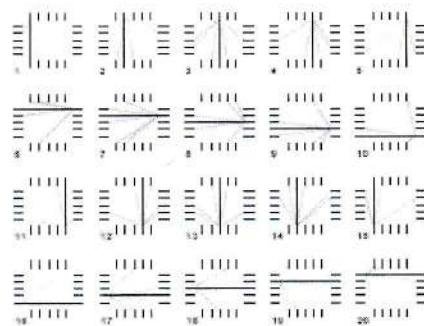

| 1.3    Convention de notation :.....                                     | 9  |

| 1.4    Représentation de l'architecture interne d'un PLD : .....         | 9  |

| 1.5    Les différentes familles de PLD : .....                           | 12 |

| 1.6    PROM .....                                                        | 12 |

| 1.7    Les PLA .....                                                     | 12 |

| 1.8    Les PAL : .....                                                   | 13 |

| 1.8.1    Principe d'un PAL :.....                                        | 14 |

| .....                                                                    | 15 |

| 1.8.2    Convention de représentation :.....                             | 15 |

| 1.8.3    Les différentes structures : .....                              | 17 |

| 1.8.4    Les différents types d'entrées /sorties : .....                 | 19 |

| 1.8.4.1    Entrées/Sorties combinatoires :.....                          | 19 |

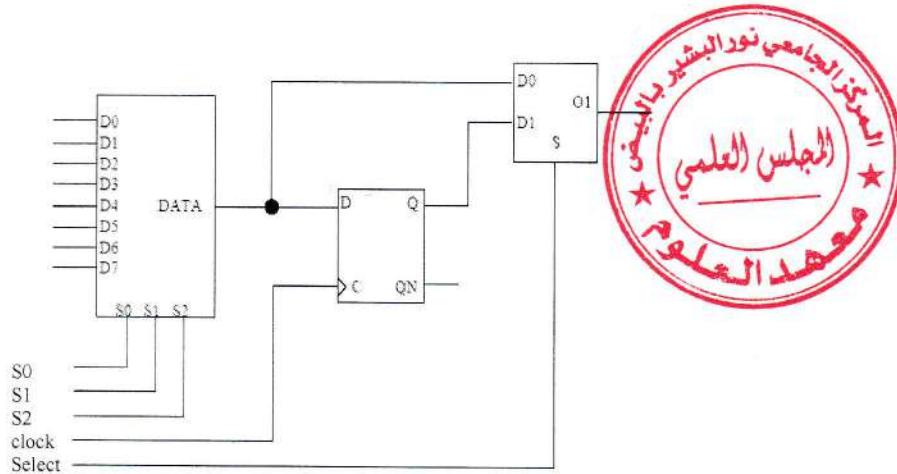

| 1.8.4.2    Séquentielle :.....                                           | 21 |

| 1.8.4.2.1    Sorties à registres PAL de type R .....                     | 21 |

| 1.8.4.2.2    Sorties à Ou Exclusif et Registre PAL de type X .....       | 23 |

| 1.8.4.2.3    Sorties à Registre asynchrone PAL de type RA .....          | 23 |

| 1.8.4.3    Sorties versatiles PAL de type V .....                        | 24 |

| 1.8.4.4    Les références des PAL.....                                   | 30 |

| 1.8.5    GAL.....                                                        | 31 |

| 1.8.6    Hard Array Logic (HAL) .....                                    | 32 |

| 1.8.7    Les EPLD : .....                                                | 32 |

| 1.8.8    LES CPLD : .....                                                | 35 |

| 1.8.8.1    Structure générale d'un CPLD :.....                           | 36 |

| 1.8.9    Les FPGA :.....                                                 | 36 |

| Chapitre 2 : Les technologies des éléments programmables.....            | 39 |

| 2.1    Les Technologies d'interconnexion :.....                          | 40 |

| 2.1.1    Les cellules à fusible : .....                                  | 40 |

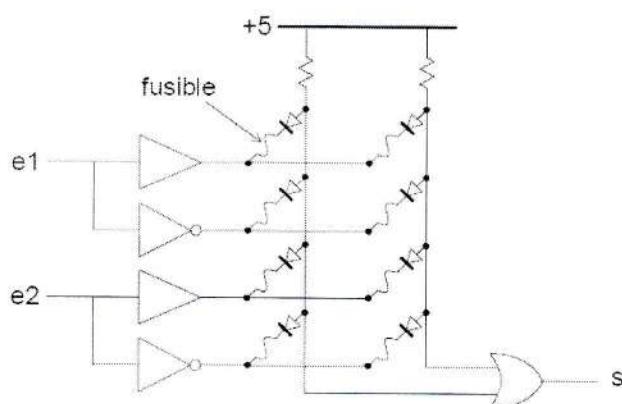

| 2.1.2    Les Cellules à anti fusible : .....                             | 41 |

| 2.1.3    Les cellules anti-fusibles à diélectrique.....                  | 41 |

| 2.1.4    Les cellules anti-fusibles en silicium amorphe .....            | 41 |

| 2.1.5    Les cellules à transistors MOS a grille flottante et EPROM..... | 42 |

|          |                                                       |    |

|----------|-------------------------------------------------------|----|

| 2.1.6    | Les Cellules UV EPROM : .....                         | 43 |

| 2.1.7    | Les Cellules EEPROM : (Electrically EPROM) .....      | 43 |

| 2.1.8    | Les Cellules Flash EEPROM : .....                     | 43 |

| 2.1.9    | Les technologies à RAM statique –SRAM .....           | 44 |

| 2.1.10   | Les Cellules SRAM a transistors MOS classique : ..... | 44 |

| 2.1.11   | Les circuits Full Custom .....                        | 47 |

| 2.1.11.1 | Les circuits à la demande : .....                     | 47 |

| 2.1.11.2 | Les circuits à base de cellules .....                 | 48 |

|          | Chapitre 3. Architecture des FPGA.....                | 54 |

| 3.1      | Les FPGA (Field Programmable Gate Array). ....        | 55 |

| 3.2      | Blocs logiques programmables.....                     | 56 |

|          | Chapitre 4. Programmation VHDL .....                  | 66 |

| 4.1      | Introduction .....                                    | 67 |

| 4.1.1    | À propos de VHDL.....                                 | 67 |

| 4.1.2    | Conception.....                                       | 68 |

| 4.1.3    | Les outils EDA .....                                  | 68 |

| 4.2      | Structure du code.....                                | 68 |

| 4.2.1    | Unités VHDL fondamentales .....                       | 68 |

| 4.2.2    | LIBRARY (bibliothèque).....                           | 69 |

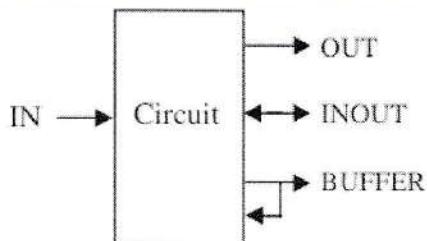

| 4.2.3    | ENTITY (entité).....                                  | 70 |

| 4.2.4    | ARCHITECTURE .....                                    | 71 |

| 4.2.5    | Exemples .....                                        | 72 |

| 4.3      | Types de données .....                                | 76 |

| 4.3.1    | Types de données prédéfinis .....                     | 76 |

| 4.3.2    | Types de données définis par l'utilisateur.....       | 80 |

| 4.3.3    | Sous-types .....                                      | 81 |

| 4.3.4    | Tableaux .....                                        | 82 |

| 4.4      | Opérateurs et attributs.....                          | 83 |

| 4.4.1    | Opérateurs.....                                       | 83 |

| 4.4.2    | Attributs définis par l'utilisateur.....              | 87 |

| 4.5      | Programmation concurrente .....                       | 88 |

| 4.5.1    | Concurrent versus séquentiel.....                     | 89 |

| 4.5.2    | Utilisation des opérateurs.....                       | 91 |

| 4.5.3    | WHEN (simple et sélectionné).....                     | 92 |

|          | Exemple 5.3 : Tampon à trois états .....              | 96 |

| 4.5.4    | GENERATE.....                                         | 96 |

| 4.5.5    | BLOCK .....                                           | 97 |

|       |                                                                                                         |     |

|-------|---------------------------------------------------------------------------------------------------------|-----|

| 4.6   | Programmation séquentiel .....                                                                          | 100 |

| 4.6.1 | PROCESS .....                                                                                           | 101 |

| 4.6.2 | Signaux et variables.....                                                                               | 102 |

| 4.6.3 | IF .....                                                                                                | 103 |

| 4.6.4 | WAIT .....                                                                                              | 103 |

| 4.6.5 | CASE.....                                                                                               | 105 |

| 4.6.6 | LOOP .....                                                                                              | 105 |

| 4.6.7 | CASE ou IF .....                                                                                        | 106 |

| 4.6.8 | CASE versus WHEN .....                                                                                  | 107 |

| 4.7   | Signaux et Variables .....                                                                              | 108 |

| 4.7.1 | CONSTANT .....                                                                                          | 108 |

| 4.7.2 | SIGNAL.....                                                                                             | 109 |

| 4.7.3 | VARIABLE.....                                                                                           | 110 |

| 4.7.4 | SIGNAL ou VARIABLE.....                                                                                 | 111 |

|       | Chapitre 5. Applications : Implémentation de quelques circuits logiques dans les circuits<br>FPGA ..... | 113 |

| 5.1   | Exemple d'implantation .....                                                                            | 114 |

| 5.1.1 | La porte « OU ».....                                                                                    | 114 |

| 5.1.2 | Demi additionneur .....                                                                                 | 129 |

## Liste des figures :

|                                                                                   |    |

|-----------------------------------------------------------------------------------|----|

| Figure 1. Structure des réseaux logiques combinatoires .....                      | 8  |

| Figure 2. Symbolisation des portes logiques pour les PLD .....                    | 8  |

| Figure 3. Symbole d'une porte AND à 3 entrées .....                               | 9  |

| Figure 4. Symbole simplifié d'une porte AND .....                                 | 9  |

| Figure 5. La sortie S réalise une fonction OU avec deux fonction AND.....         | 9  |

| Figure 6. Structure de base d'un PLD .....                                        | 10 |

| Figure 7. Structure de base avec les normes des constructeurs .....               | 10 |

| Figure 8. Structure après programmation.....                                      | 10 |

| Figure 9. Structure logique d'une PROM bipolaire à fusibles .....                 | 11 |

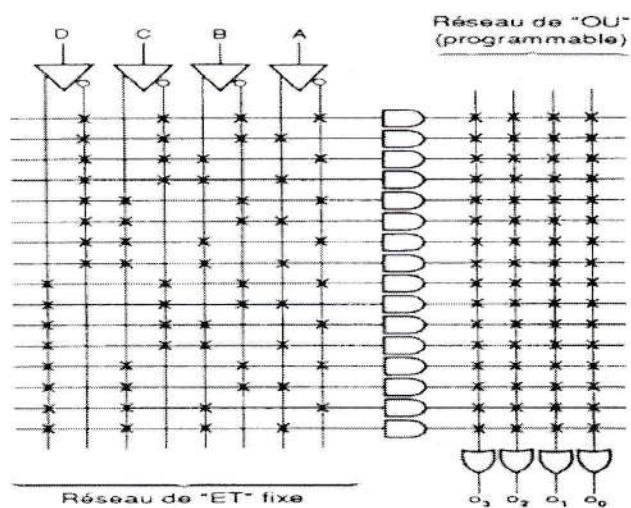

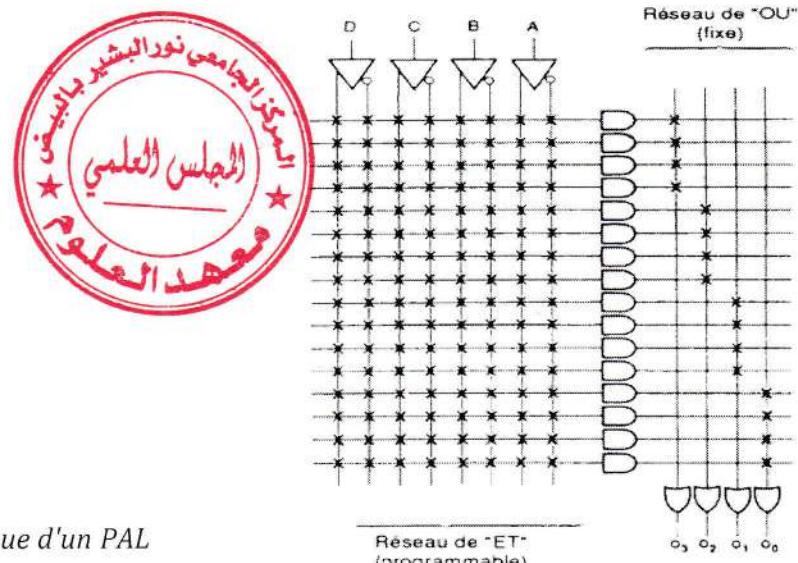

| Figure 10. Structure logique d'un PLA .....                                       | 13 |

| Figure 11. Structure simplifié d'un PAL.....                                      | 15 |

| Figure 12. Symbole simplifié d'un PAL .....                                       | 15 |

| Figure 13. Exemple de programmation d'un PAL .....                                | 15 |

| Figure 14. Structure de base d'un PAL.....                                        | 16 |

| Figure 15. Porte à sortie 3 états.....                                            | 16 |

| Figure 16. Structure logique d'un PAL .....                                       | 17 |

| Figure 17. Schema synoptique d'un PAL .....                                       | 18 |

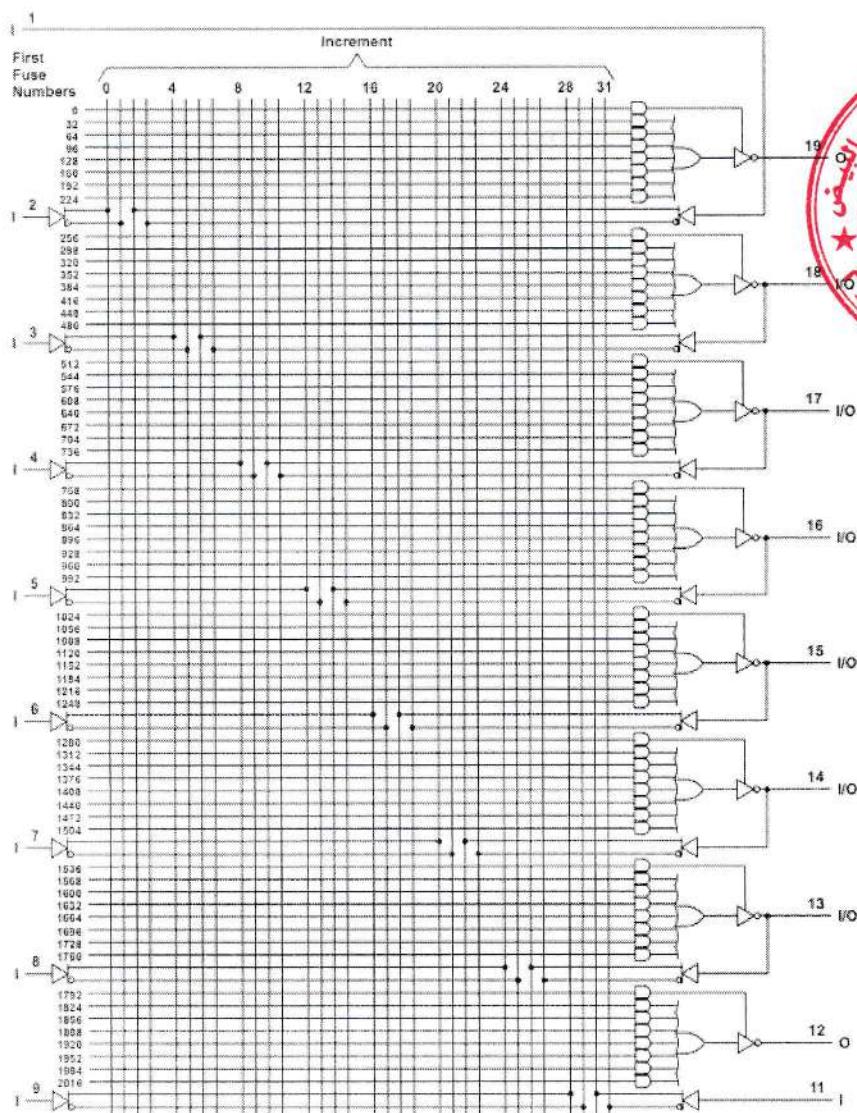

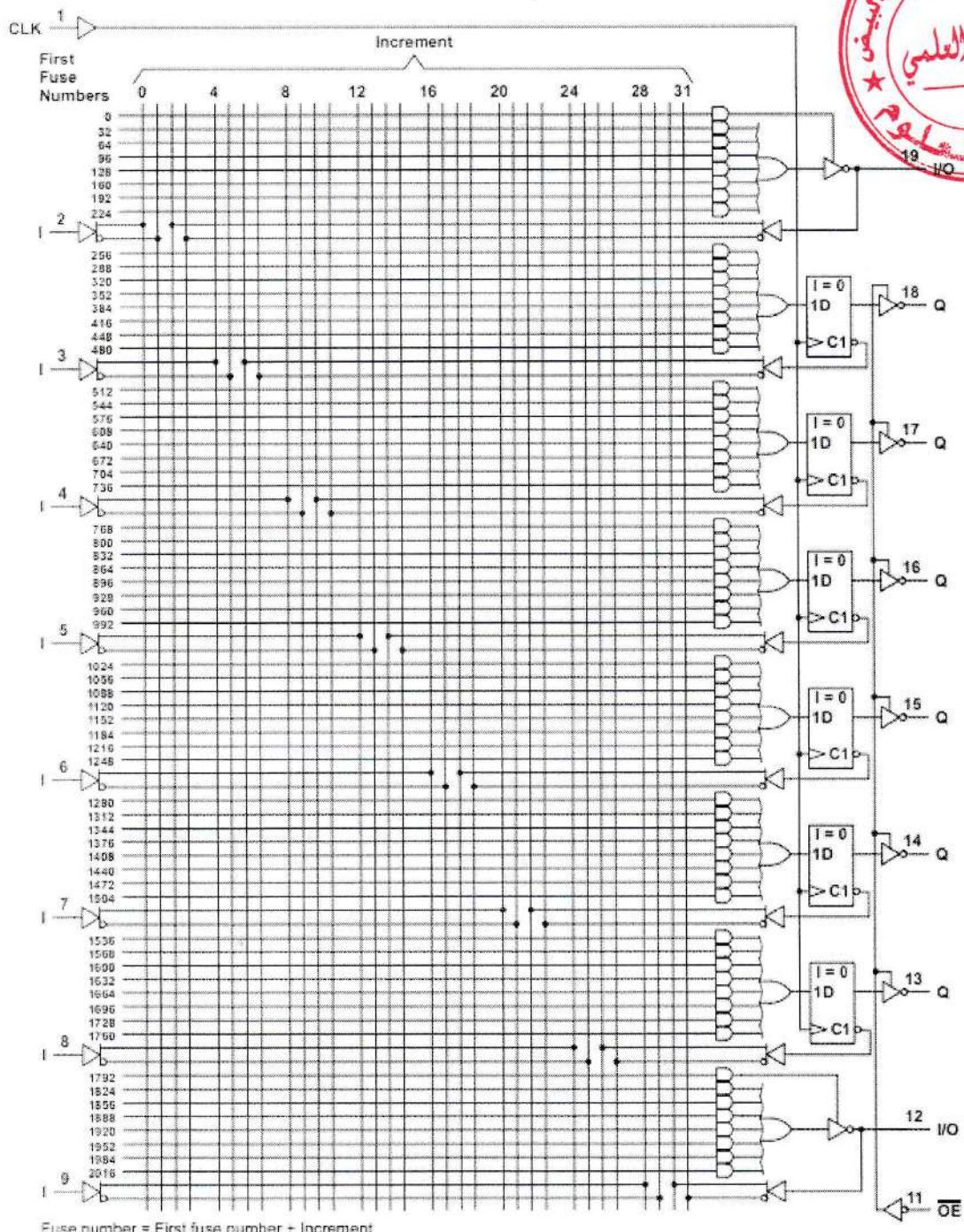

| Figure 18. PAL16L8 .....                                                          | 20 |

| Figure 19. PAL combiné .....                                                      | 20 |

| Figure 20. PAL type R .....                                                       | 21 |

| Figure 21.PAL16R6 .....                                                           | 22 |

| Figure 22. PAL type X .....                                                       | 23 |

| Figure 23. PAL type RA .....                                                      | 23 |

| Figure 24. Différentes configurations .....                                       | 23 |

| Figure 25. PAL à registre 16R8 .....                                              | 24 |

| Figure 26. Macro cellule de PALCE16V8.....                                        | 27 |

| Figure 27. PALCE16V8 .....                                                        | 28 |

| Figure 28. Différentes configurations de la macrocellule .....                    | 29 |

| Figure 29. Macrocellule d'un EPLD.....                                            | 33 |

| Figure 30. Macro cellule configurable.....                                        | 34 |

| Figure 31. Macrocellule d'un CPLD .....                                           | 36 |

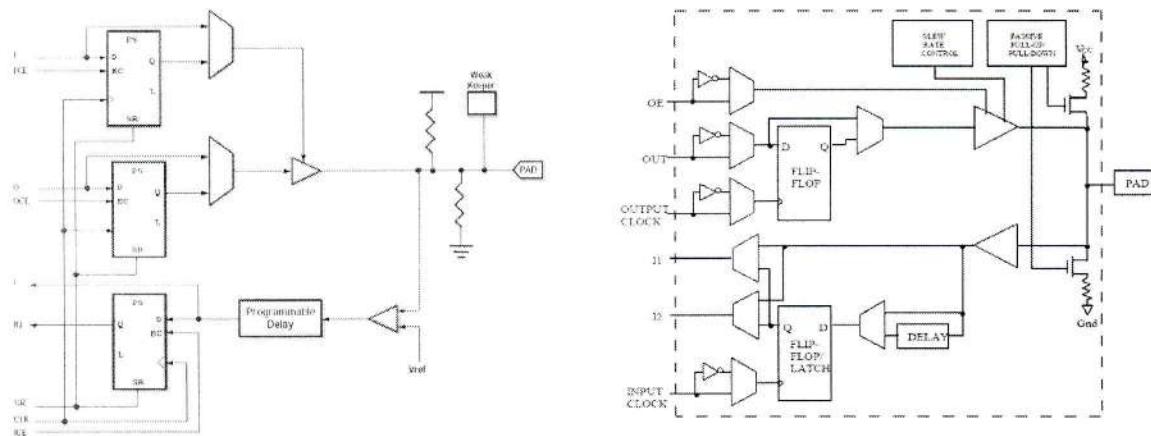

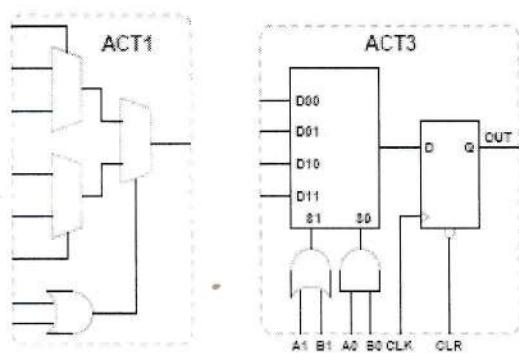

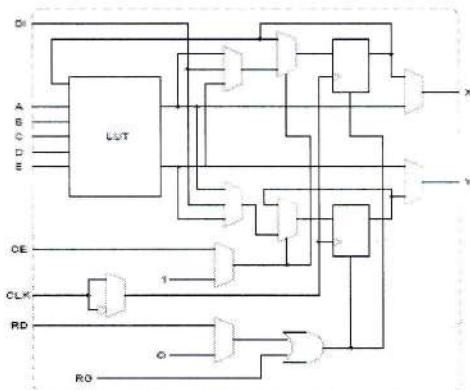

| Figure 32. Cellule de base d'un FPGA .....                                        | 37 |

| Figure 33. Structure d'un FPGA de type Xilinx .....                               | 38 |

| Figure 34. Cellule élémentaire d'un PLD à fusibles .....                          | 40 |

| Figure 35. Cellule antifusible à diélectrique .....                               | 41 |

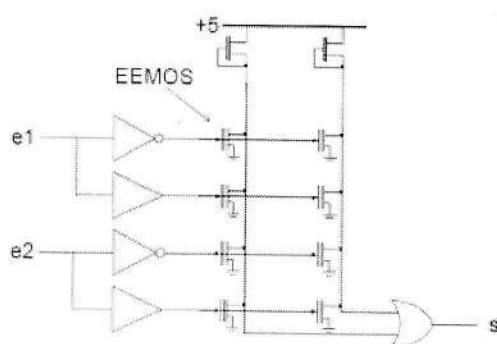

| Figure 36. PLD simple a MOS .....                                                 | 42 |

| Figure 37. Caractéristique $I_D=f(V_{GS})$ pour effacement et programmation ..... | 43 |

| Figure 38. Cellule EEPROM .....                                                   | 43 |

| Figure 39. Cellule Flash EEPROM .....                                             | 44 |

| Figure 40. Cellule SRAM .....                                                     | 45 |

| Figure 41. Cellule SRAM à 6 transistors.....                                      | 45 |

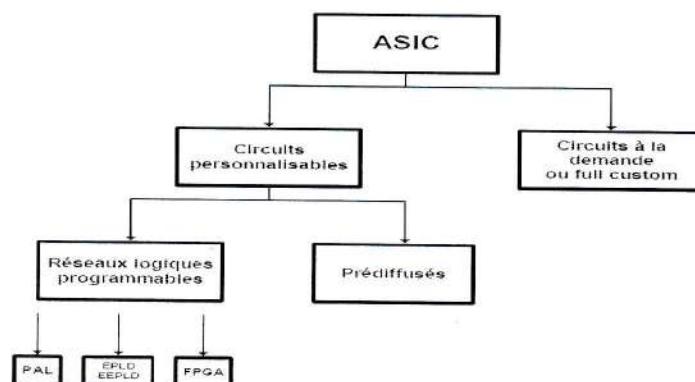

| Figure 42. Famille ASIC .....                                                     | 46 |

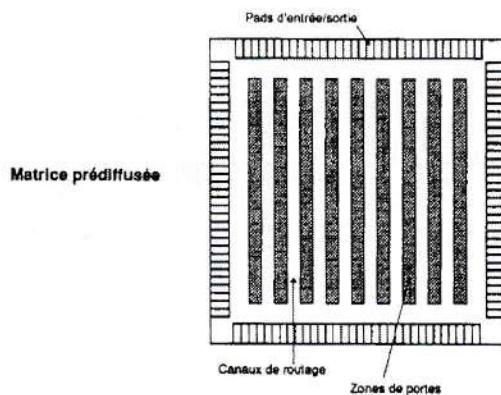

| Figure 43. Matrice prédiffusée .....                                              | 49 |

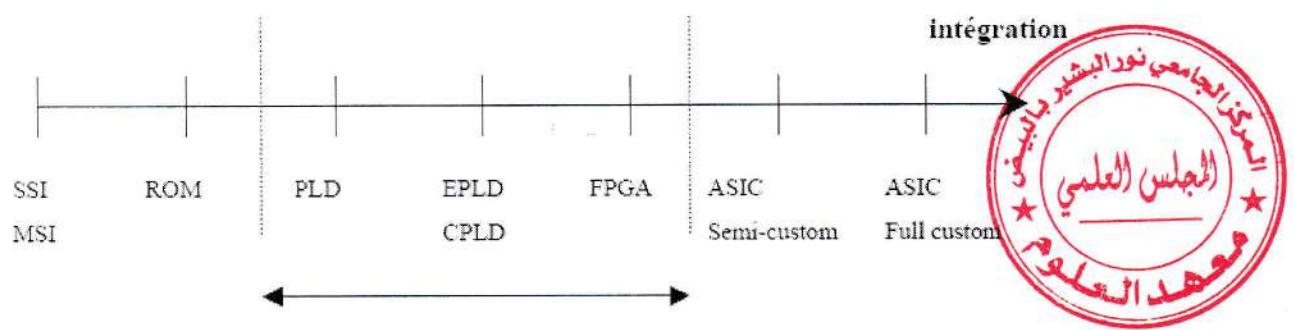

| Figure 44. Circuits Logiques Programmables par L'utilisateur .....                | 51 |

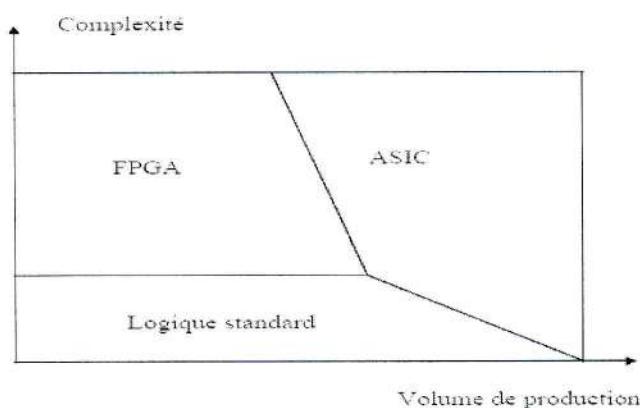

| Figure 45. Complexité (nombre de portes) / volume de production .....             | 51 |

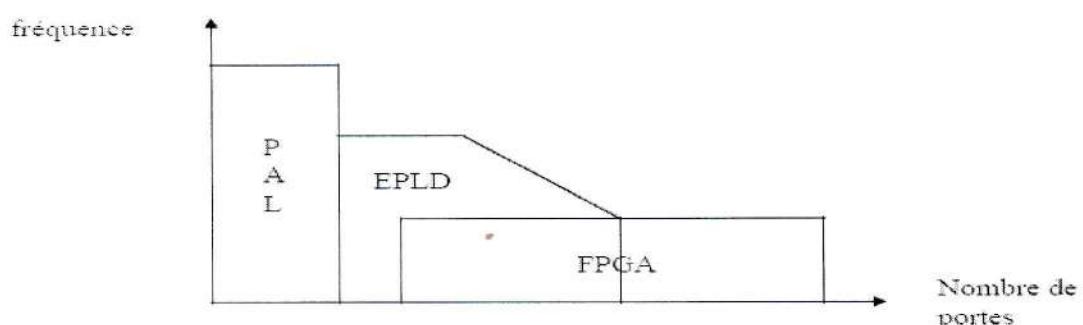

| Figure 46. Fréquence utile/nombre de portes .....                                 | 51 |

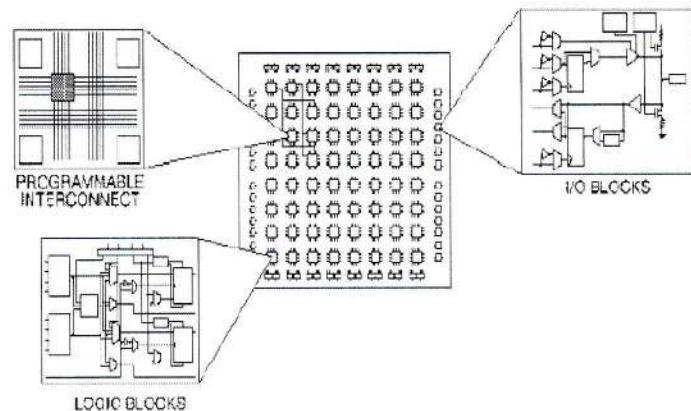

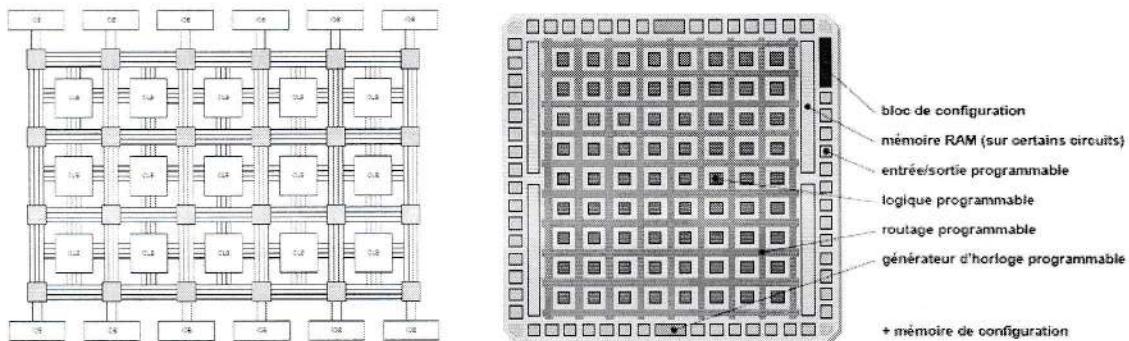

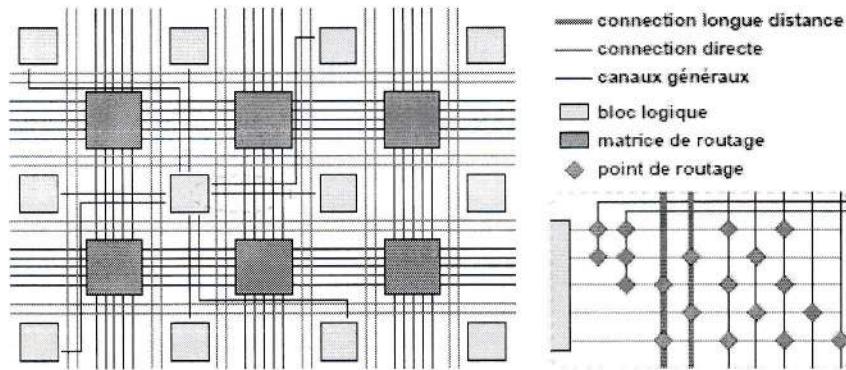

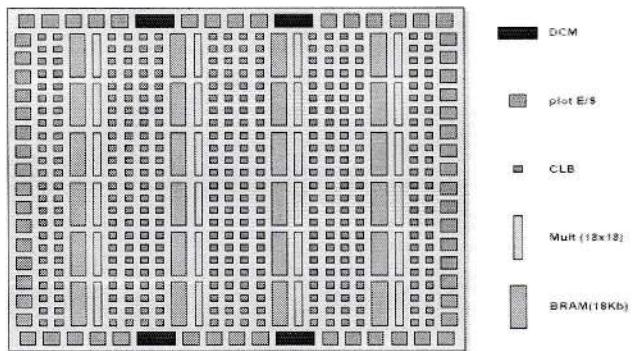

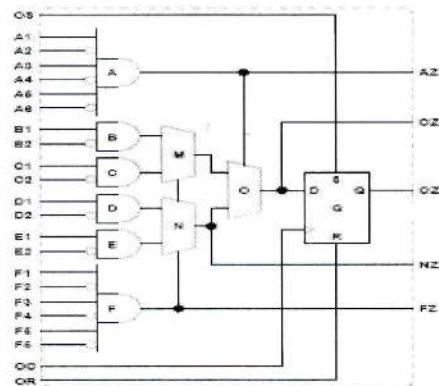

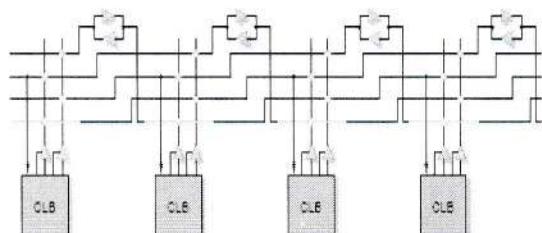

| Figure 47. Structure d'une FPGA .....                                             | 55 |

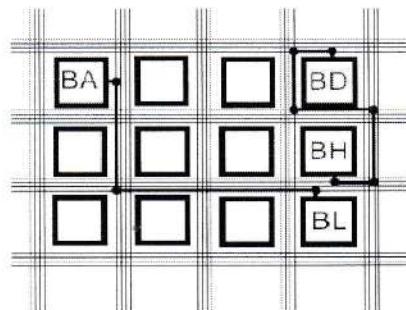

| Figure 48. Liaison entre de bloc logique .....                                    | 55 |

|                                                                                               |     |

|-----------------------------------------------------------------------------------------------|-----|

| Figure 49. Architecture d'un FPGA .....                                                       | 56  |

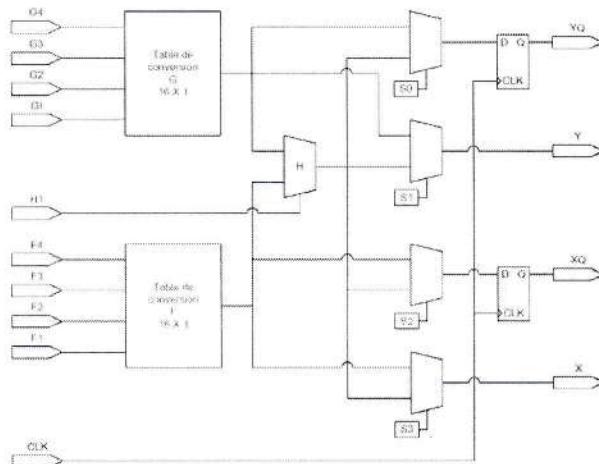

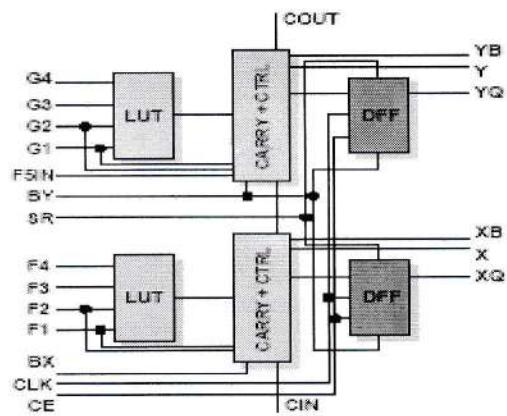

| Figure 50. Bloc logique programmable simplifié – Xilinx .....                                 | 57  |

| Figure 51. Bloc logique de base .....                                                         | 58  |

| Figure 52. Cellule I/O (IOB) .....                                                            | 59  |

| Figure 53. Structure générale du routage .....                                                | 60  |

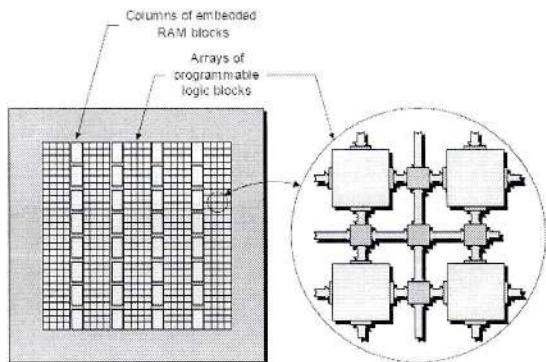

| Figure 54. Mémoire RAM intégrée .....                                                         | 61  |

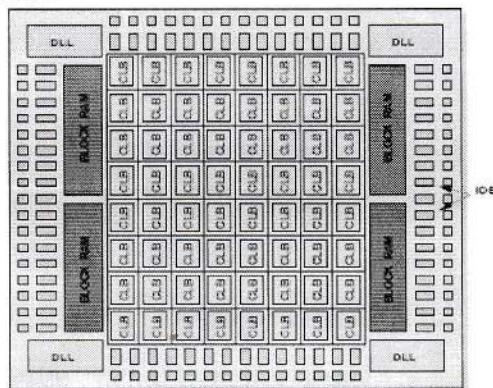

| Figure 55. Spartan II E : vue globale .....                                                   | 61  |

| Figure 56. Architecture Actel de base .....                                                   | 62  |

| <i>Figure 57. Xilinx Virtex II.....</i>                                                       | 62  |

| Figure 58. Blocs logiques Actel .....                                                         | 62  |

| Figure 59. Bloc logique Quicklogic .....                                                      | 63  |

| Figure 60. Bloc logique Xilinx Spartan II E .....                                             | 63  |

| Figure 61. Bloc logique Xilinx 3000 .....                                                     | 63  |

| Figure 62. Routage (Xilinx Spartan II E) .....                                                | 64  |

| Figure 63. Routage (Xilinx 3000) .....                                                        | 64  |

| Figure 64. Routage dans un Virtex II .....                                                    | 65  |

| Figure 65. Signal BUFFER .....                                                                | 71  |

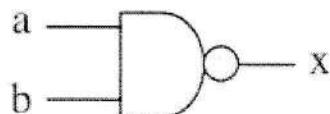

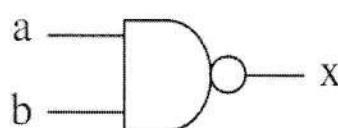

| Figure 66. Porte NAND .....                                                                   | 71  |

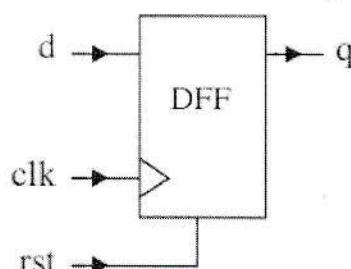

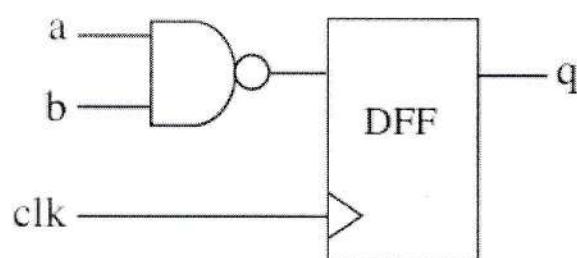

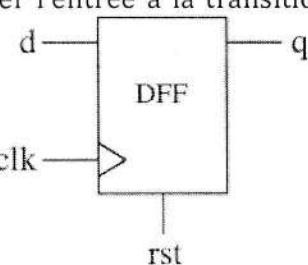

| Figure 67. Bascule D .....                                                                    | 72  |

| Figure 68. Porte NAND .....                                                                   | 72  |

| Figure 69. Bascule D avec porte NAND .....                                                    | 74  |

| Figure 70. Construction de tableaux de données .....                                          | 82  |

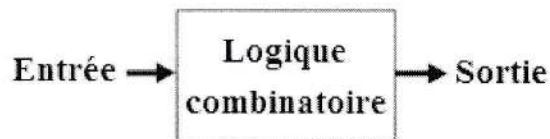

| Figure 71. Schéma synoptique de la logique combinatoire .....                                 | 89  |

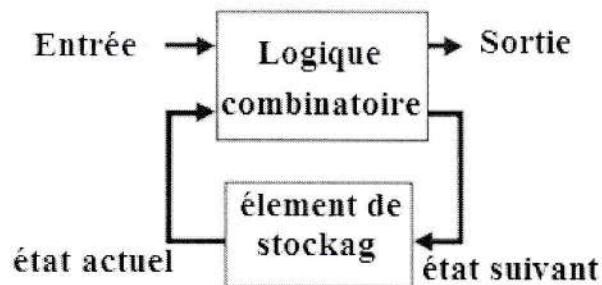

| Figure 72. Schéma synoptique de la logique séquentiel .....                                   | 89  |

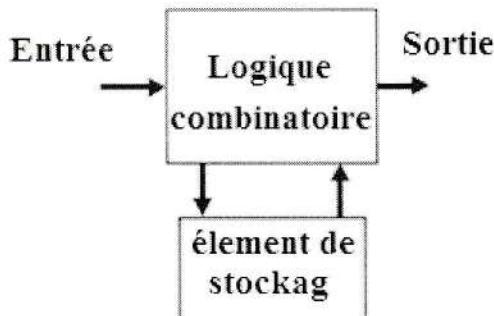

| Figure 73. Schéma synoptique de la logique combinatoire (RAM) .....                           | 90  |

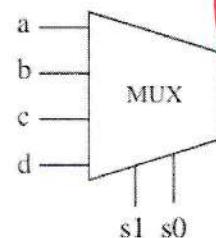

| Figure 74. Multiplexeur 4x1 .....                                                             | 92  |

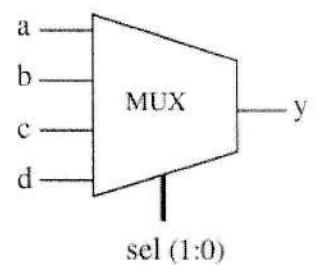

| Figure 75. MUX 2b .....                                                                       | 94  |

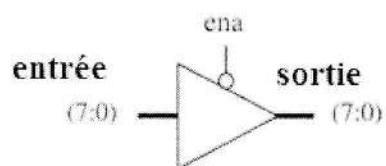

| Figure 76. Tampon à trois états .....                                                         | 95  |

| Figure 77. Bascule D .....                                                                    | 101 |

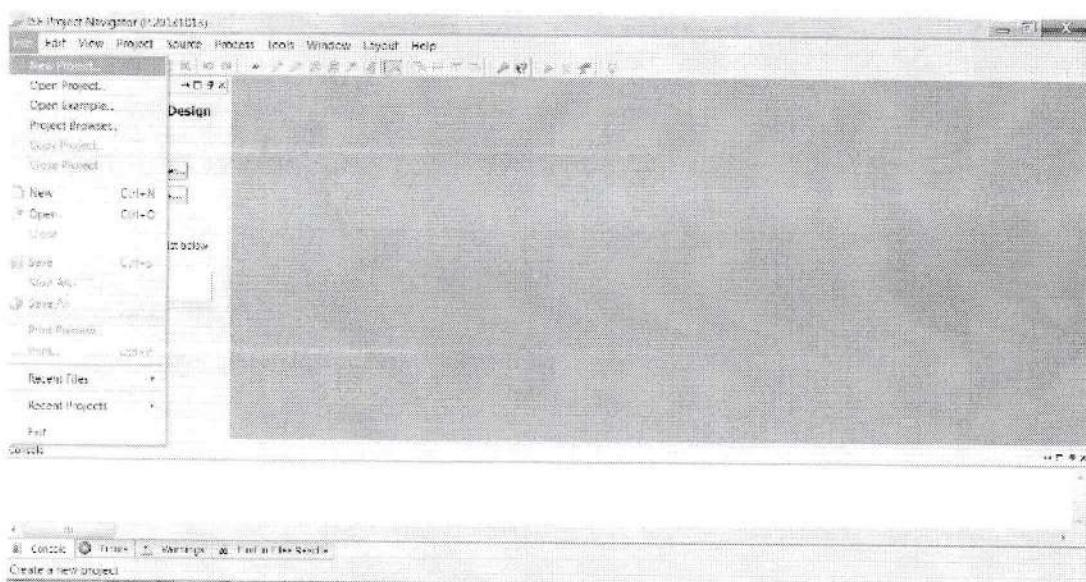

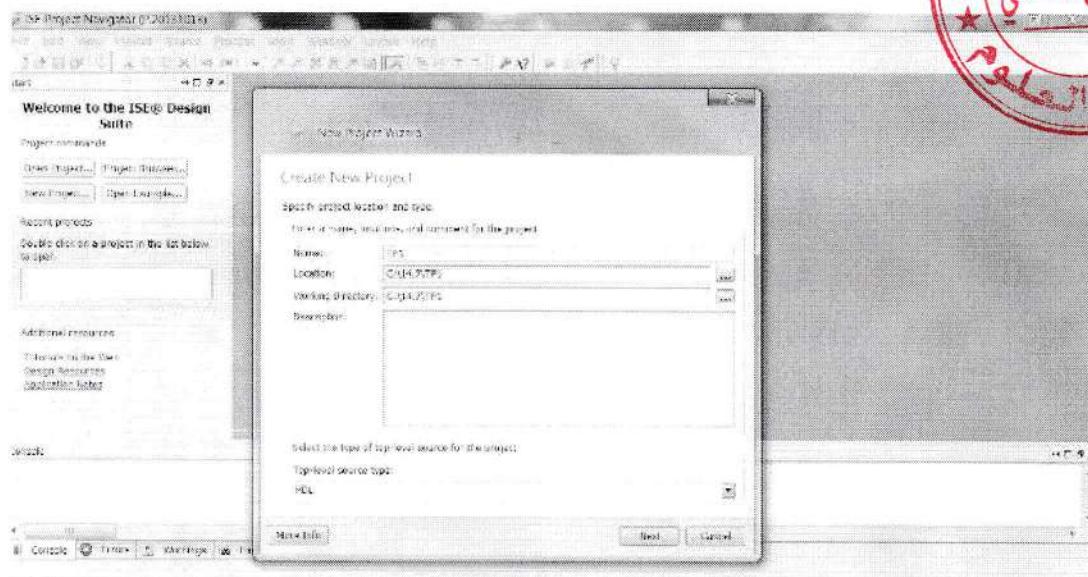

| Figure 78. Création d'un nouveau projet .....                                                 | 114 |

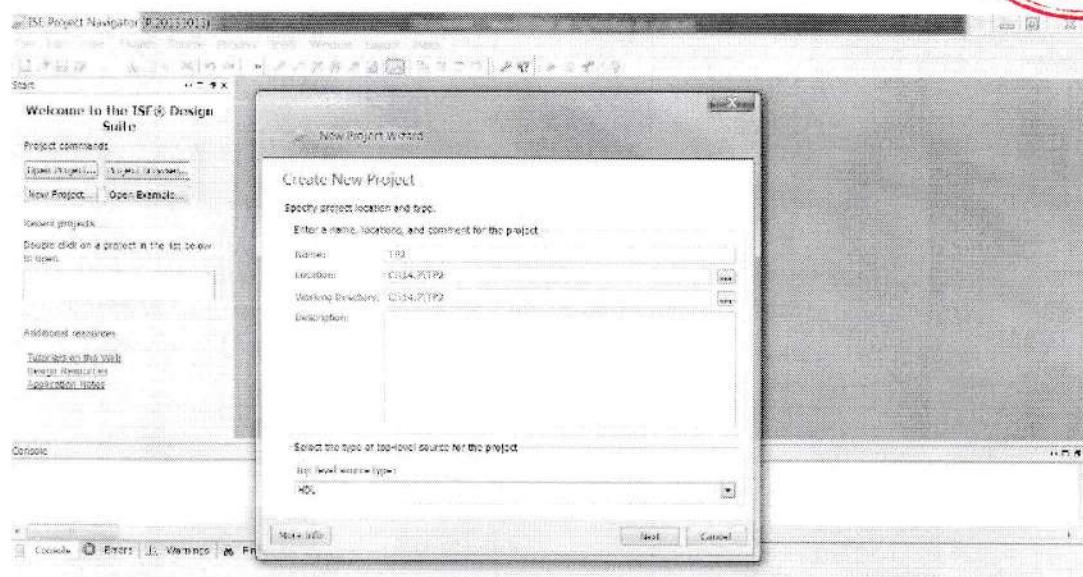

| Figure 79. Fenêtre pour introduire le nom et l'emplacement du nouveau projet .....            | 115 |

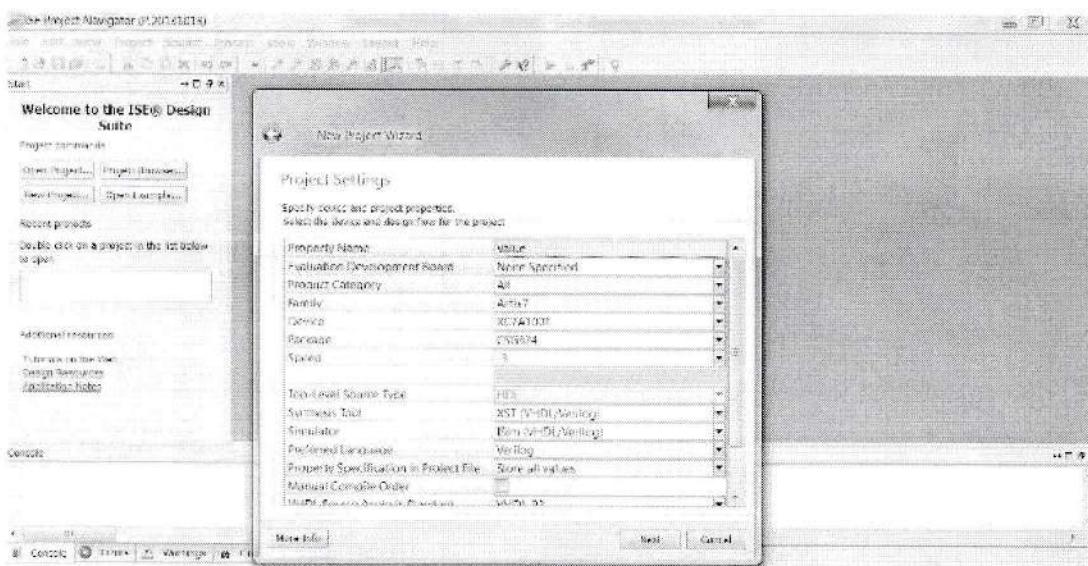

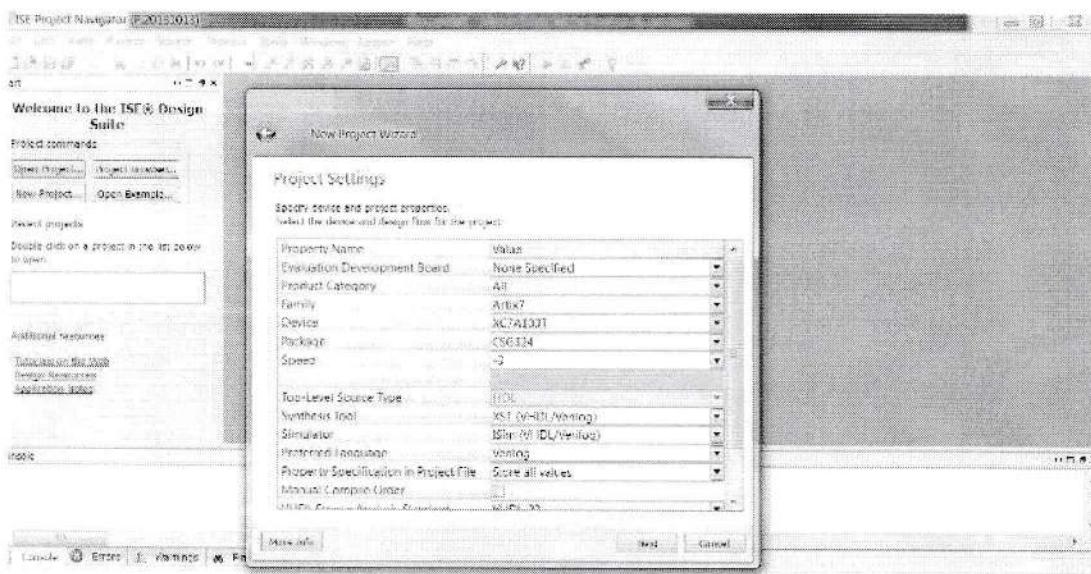

| Figure 80. Fenêtre pour les paramètres du projet .....                                        | 115 |

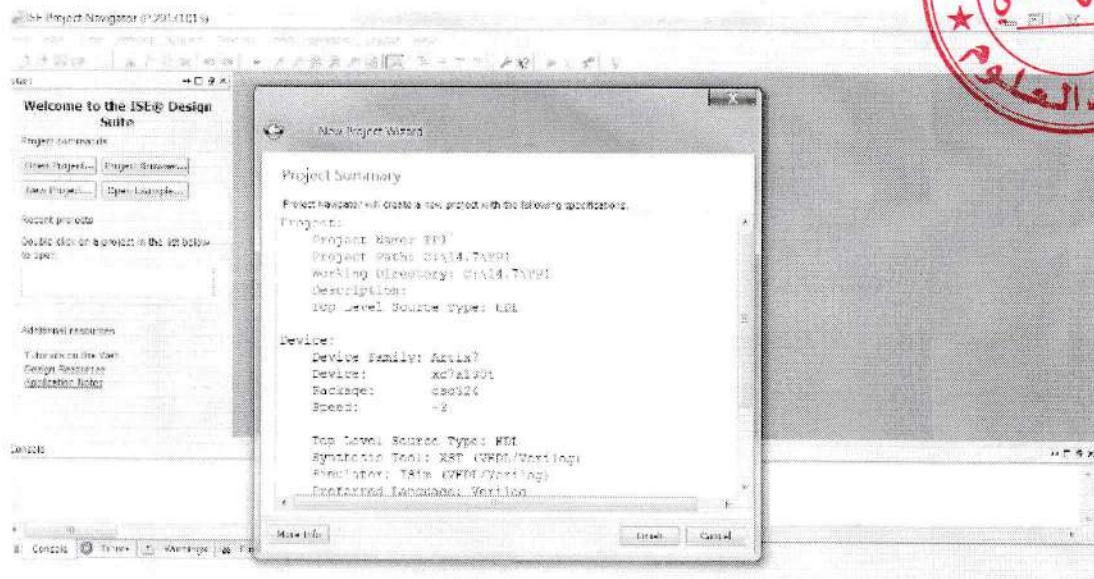

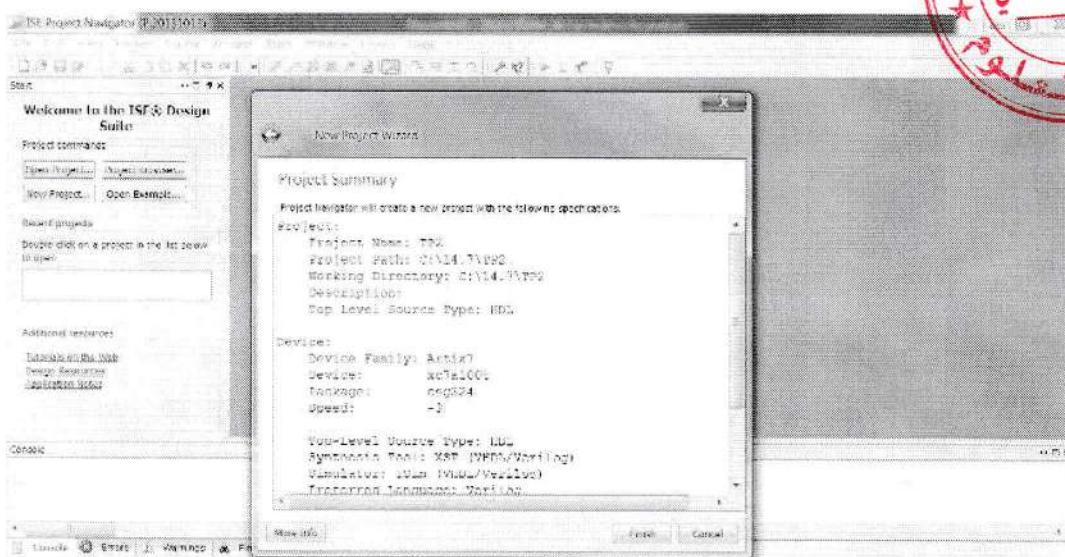

| Figure 81. Fenêtre résumant les différentes options du projet .....                           | 116 |

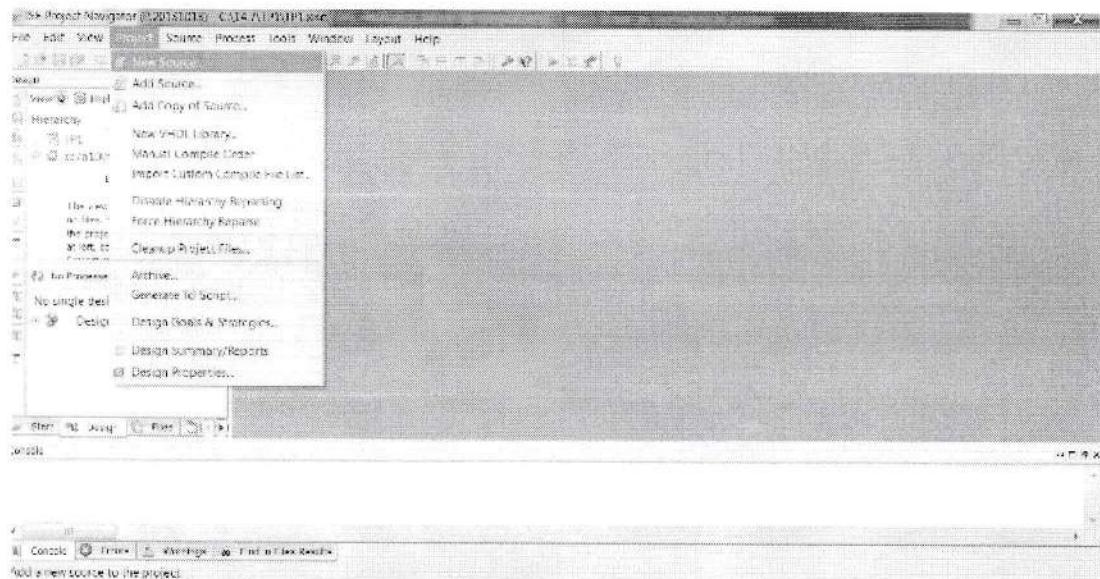

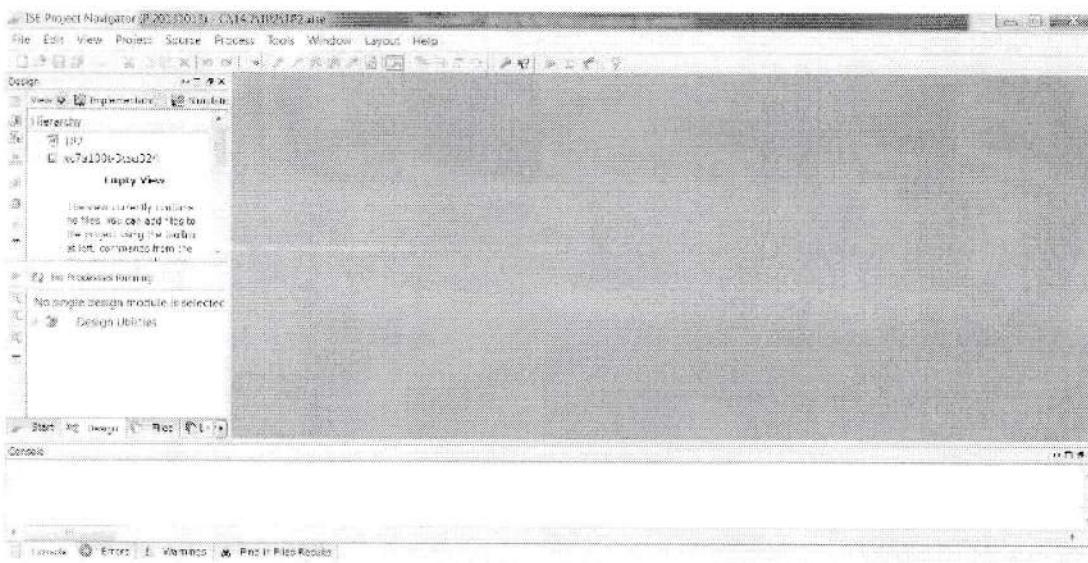

| Figure 82. La création de type de programmation .....                                         | 116 |

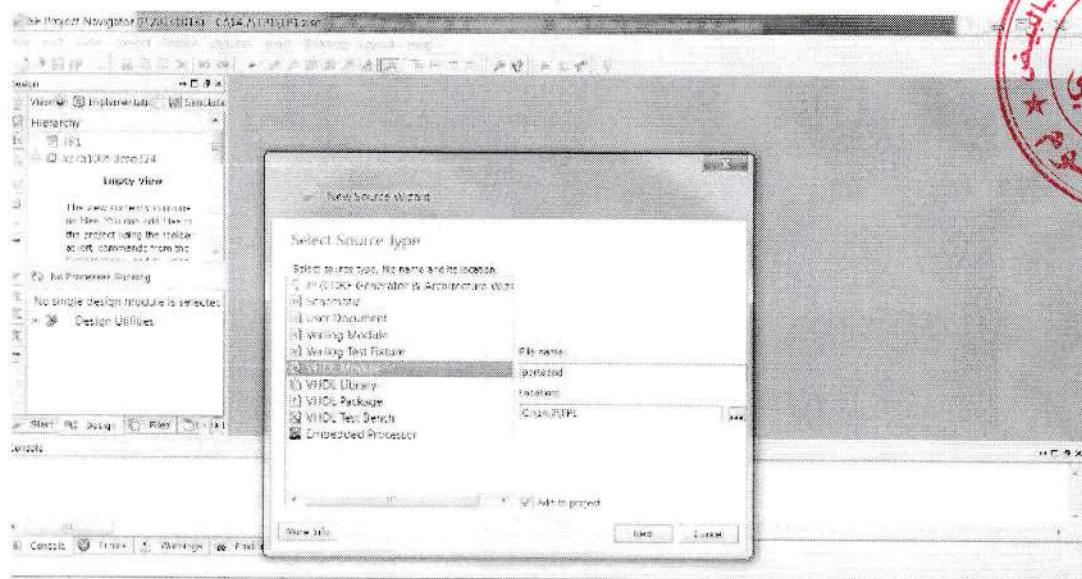

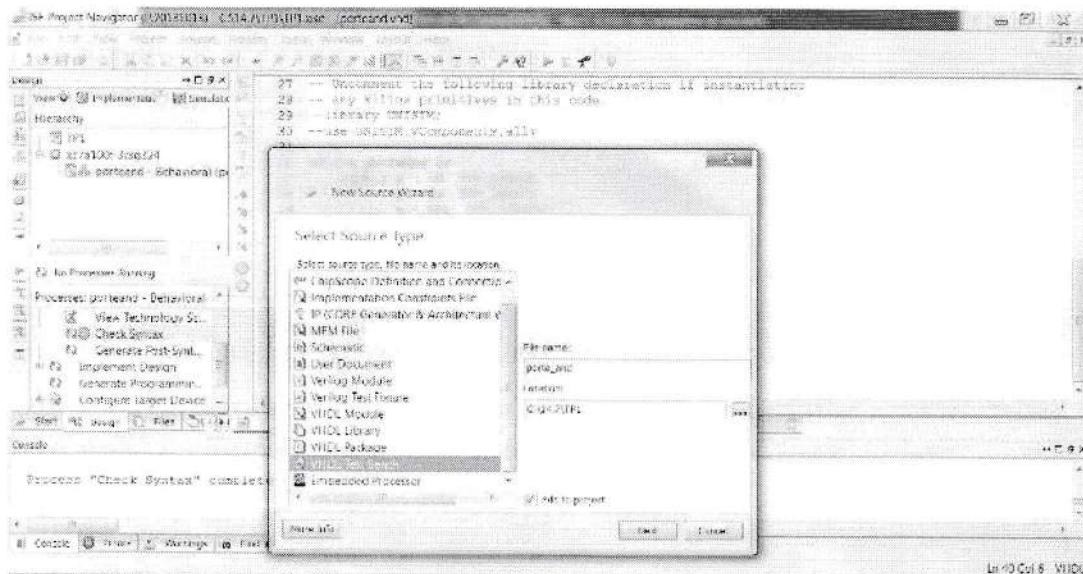

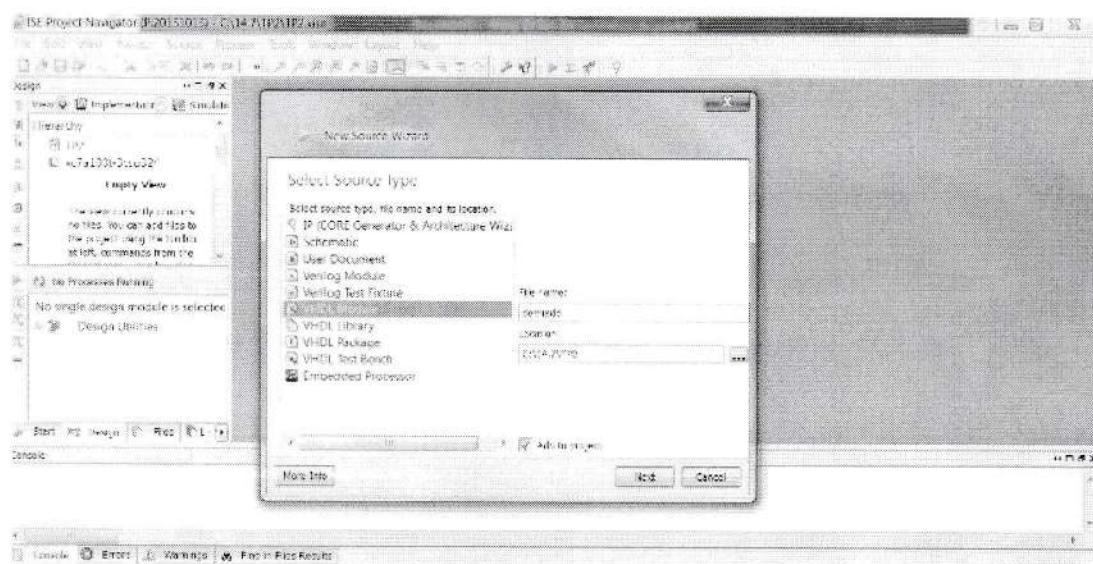

| Figure 83. Fenêtre montre les différents types de source (programmation) .....                | 117 |

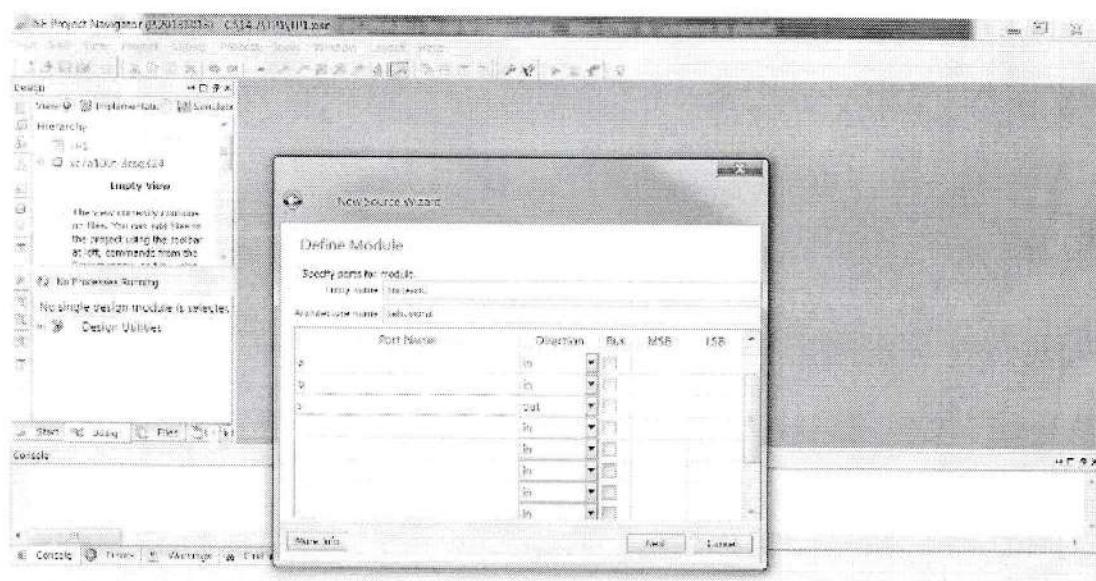

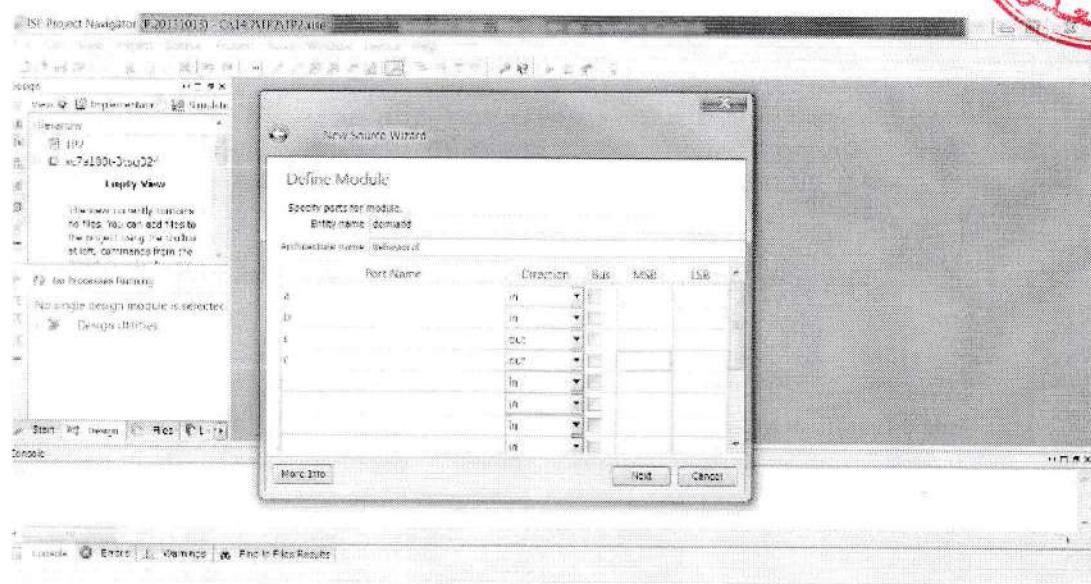

| Figure 84. Introduction des entrées et sorties dans la fenêtre ( <b>Define Module</b> ) ..... | 117 |

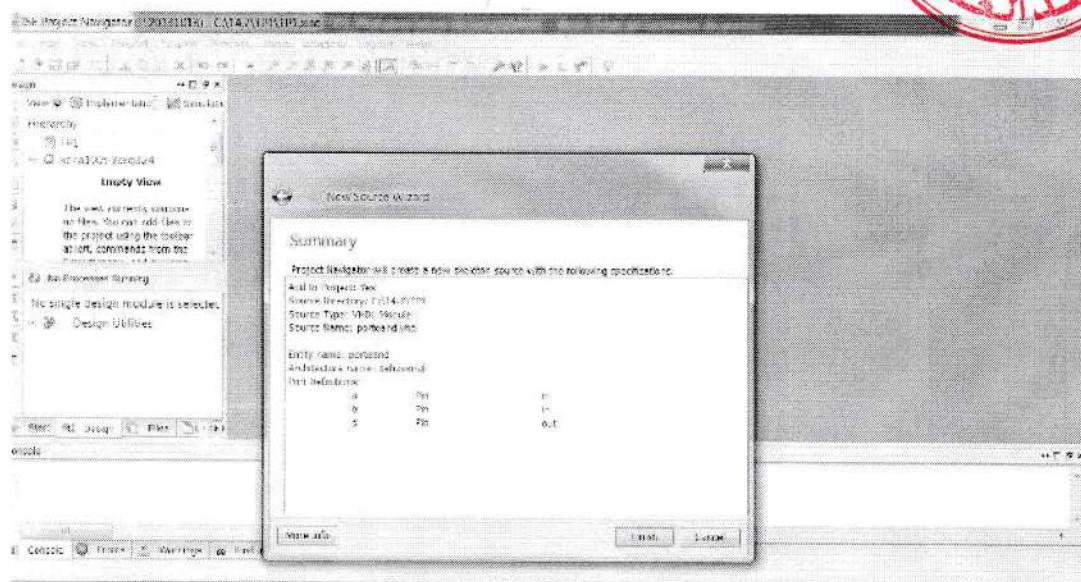

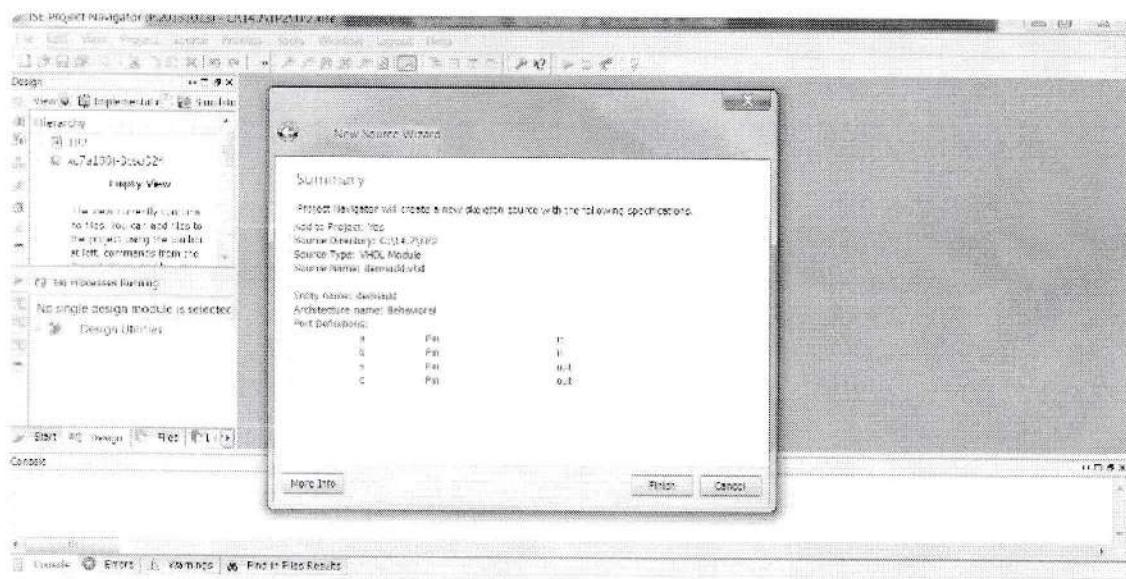

| Figure 85. Récapitulation des entrées et sorties .....                                        | 118 |

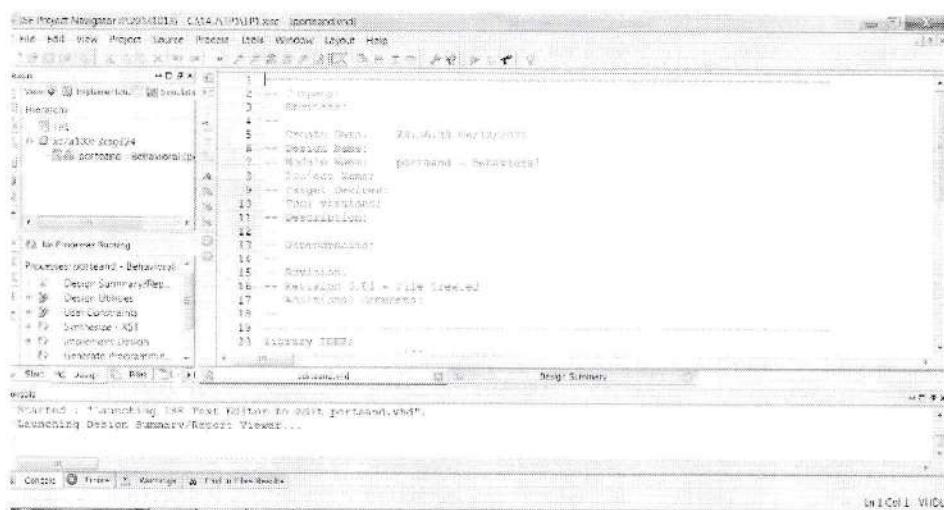

| Figure 86. La création du fichier <b>porteand.vhd</b> .....                                   | 118 |

| Figure 87. Le fichier <b>porteand.vhd</b> compléter .....                                     | 120 |

| Figure 88. Le fichier <b>porteand.vhd</b> après <b>Check Syntax</b> .....                     | 120 |

| Figure 89. Le fichier <b>porteand.vhd</b> après <b>Synthesize-XST</b> .....                   | 121 |

| Figure 90. Création de fichier de type <b>VHDL Test Bench</b> .....                           | 121 |

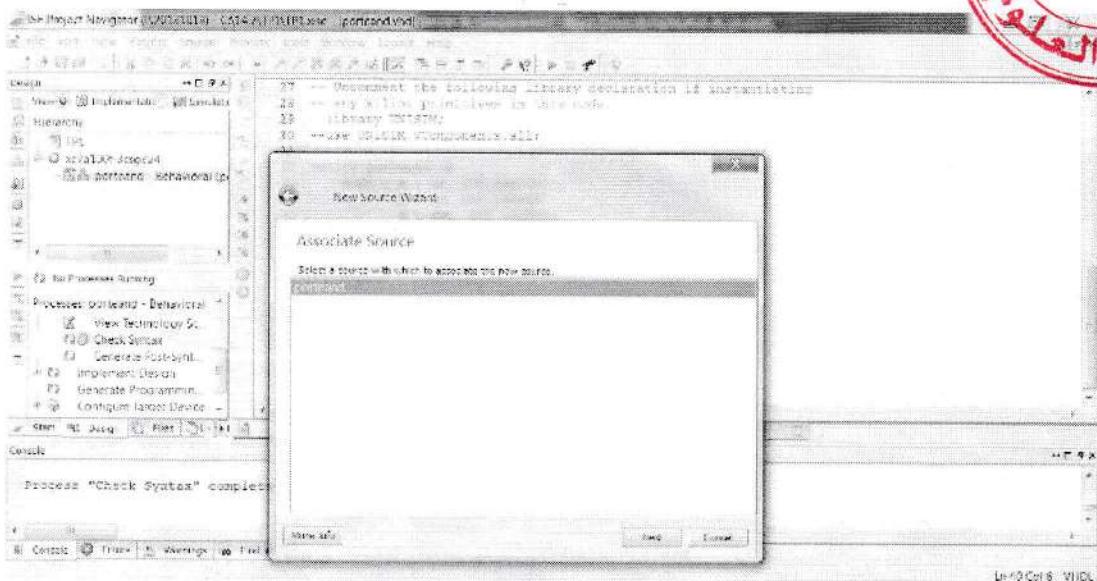

| Figure 91. Fenêtre confirmant association des deux fichiers .....                             | 122 |

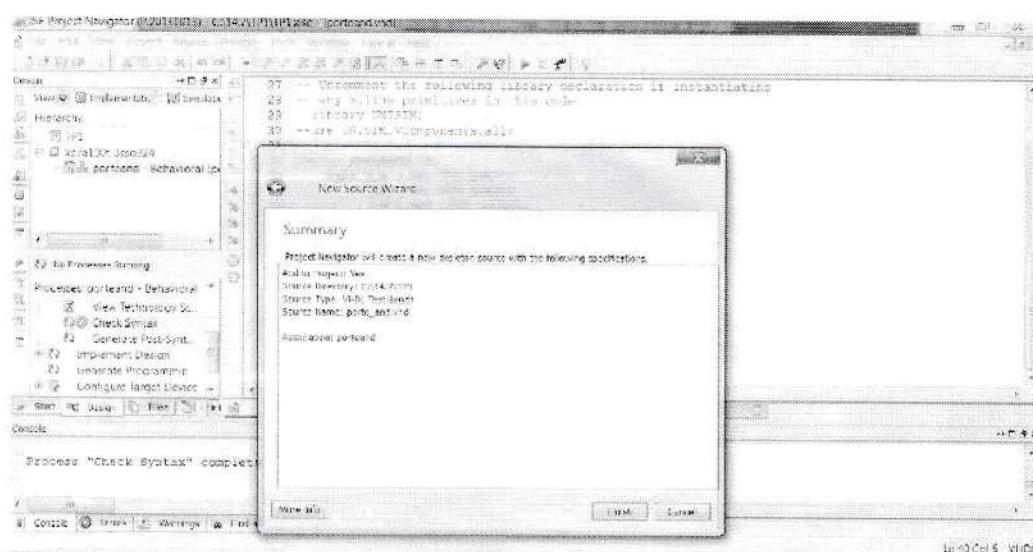

| Figure 92. Récapitulation de l'association des deux fichiers .....                            | 122 |

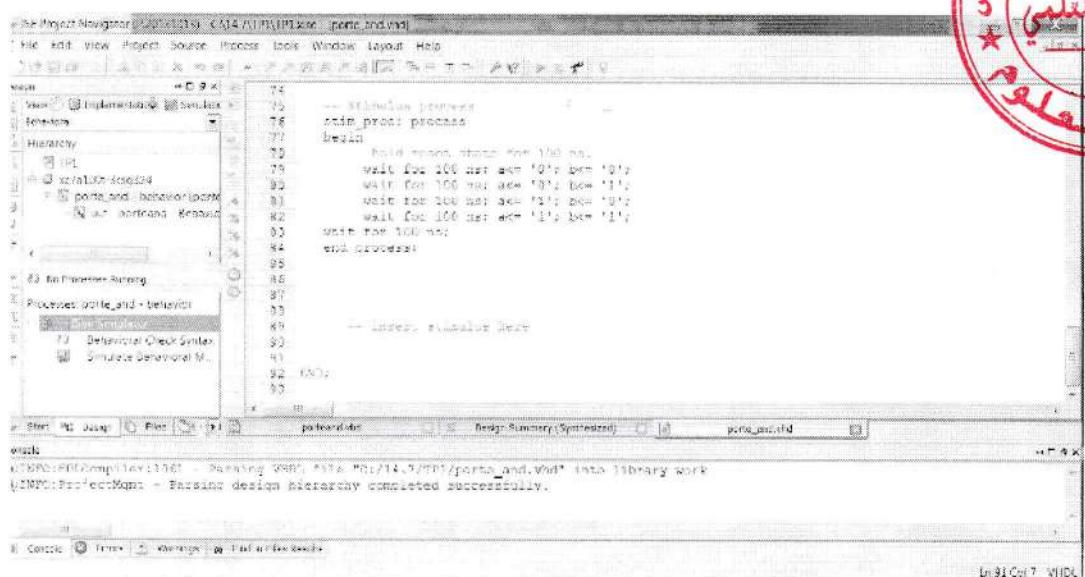

| Figure 93. Le fichier <b>VHDL Test Bench</b> est créé avec succès .....                       | 123 |

| Figure 94. Le fichier <b>porte_and.vhd</b> après modification .....                           | 125 |

| Figure 95. Changement en mode Simulation (la case Simulation coché) .....                     | 126 |

| Figure 96. Le fichier <b>porte_and.vhd</b> compléter .....                                    | 126 |

| Figure 97. <b>ISim Simulator</b> sélectionné .....                                            | 127 |

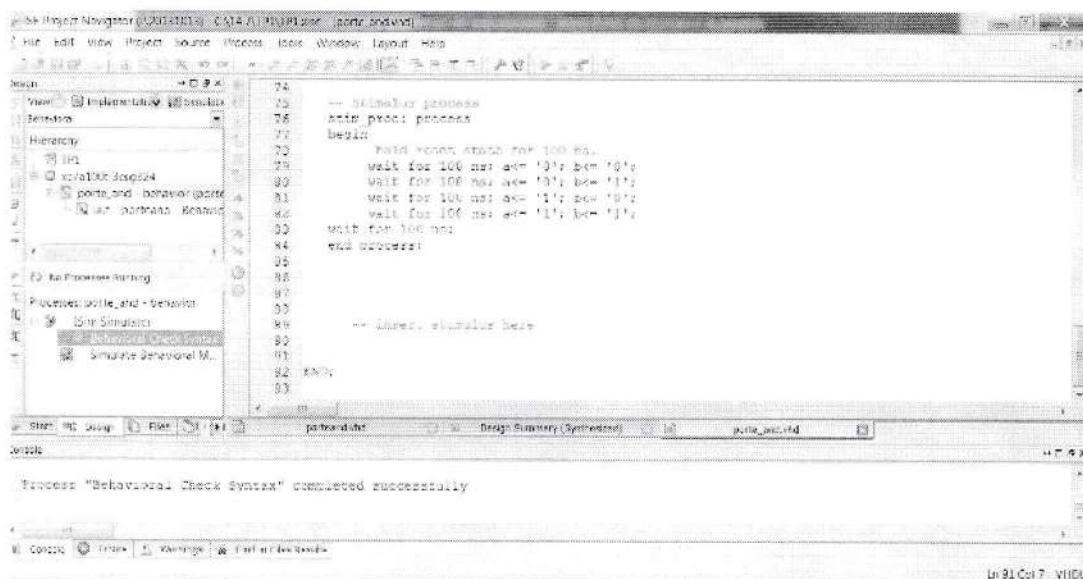

| Figure 98. Fenêtre montrant qu'il n'y a pas erreurs (verte) .....                             | 127 |

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

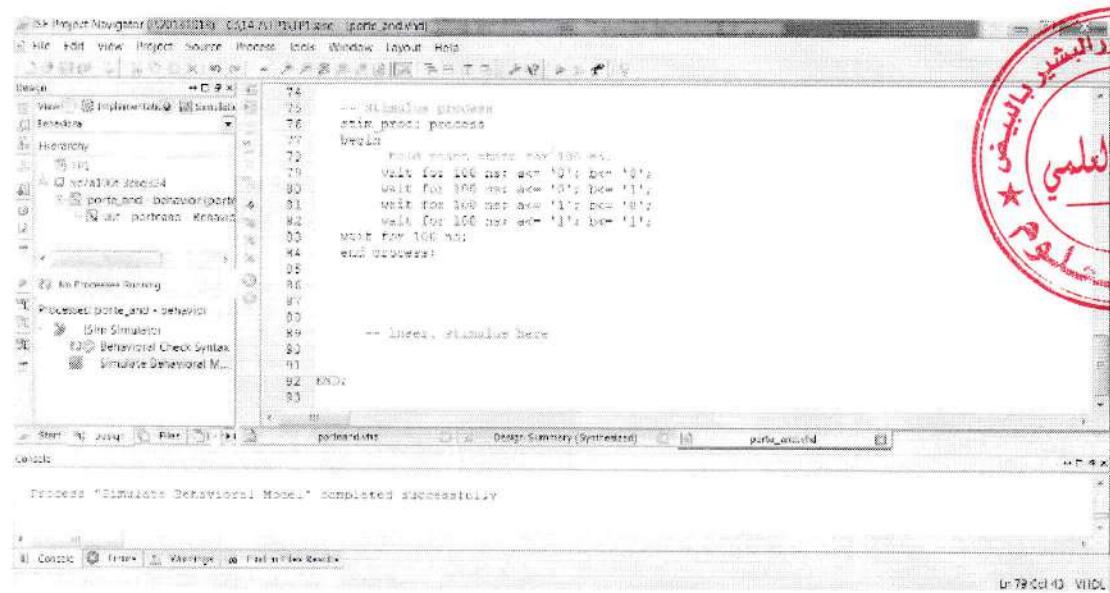

| Figure 99. Le model de simulation est compléter .....                            | 128 |

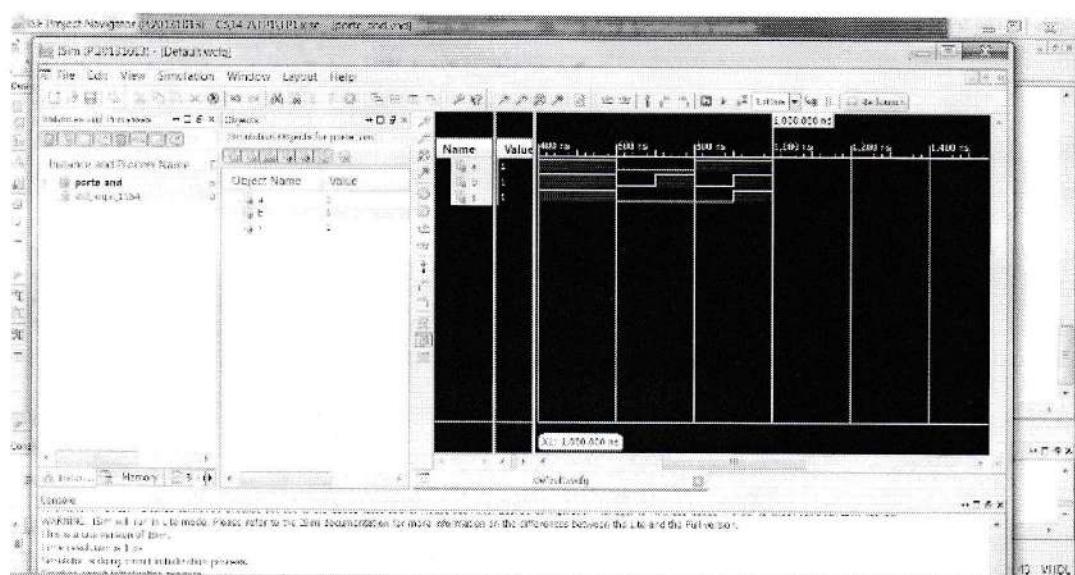

| Figure 100. Chronogramme des entrées et sorties .....                            | 128 |

| Figure 101. Création d'un nouveau projet TP2.....                                | 129 |

| Figure 102. Les différentes configurations du nouveau projet.....                | 129 |

| Figure 103. Résumé pour les différentes configurations.....                      | 130 |

| Figure 104. Création du nouveau projet.....                                      | 130 |

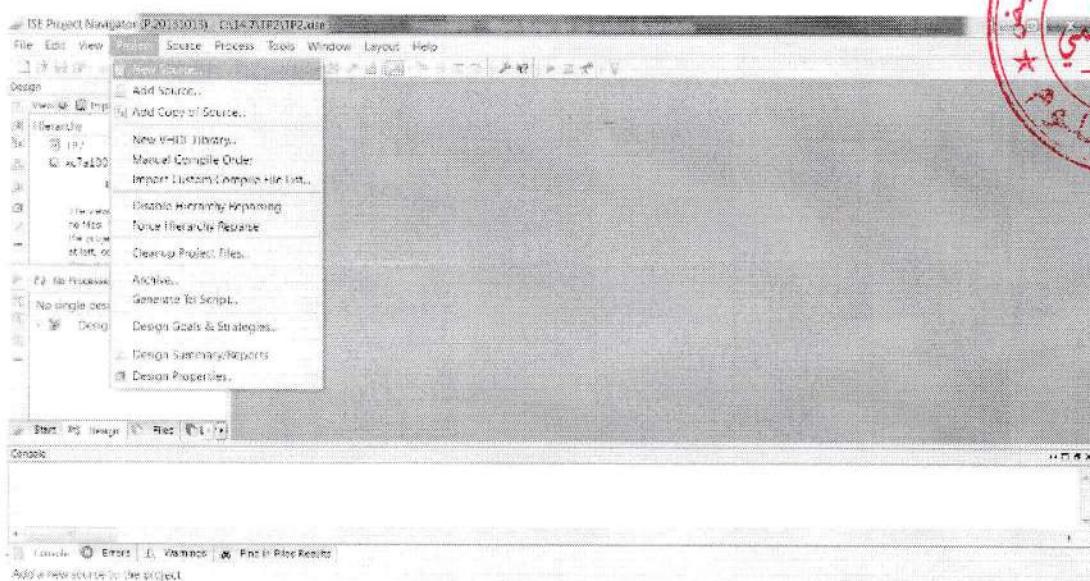

| Figure 105. Création d'une nouvelle source de programmation.....                 | 131 |

| Figure 106. Choix de type de source .....                                        | 131 |

| Figure 107. Configuration des entrées et sorties .....                           | 132 |

| Figure 108. Récapitulation du fichier VHDL.....                                  | 132 |

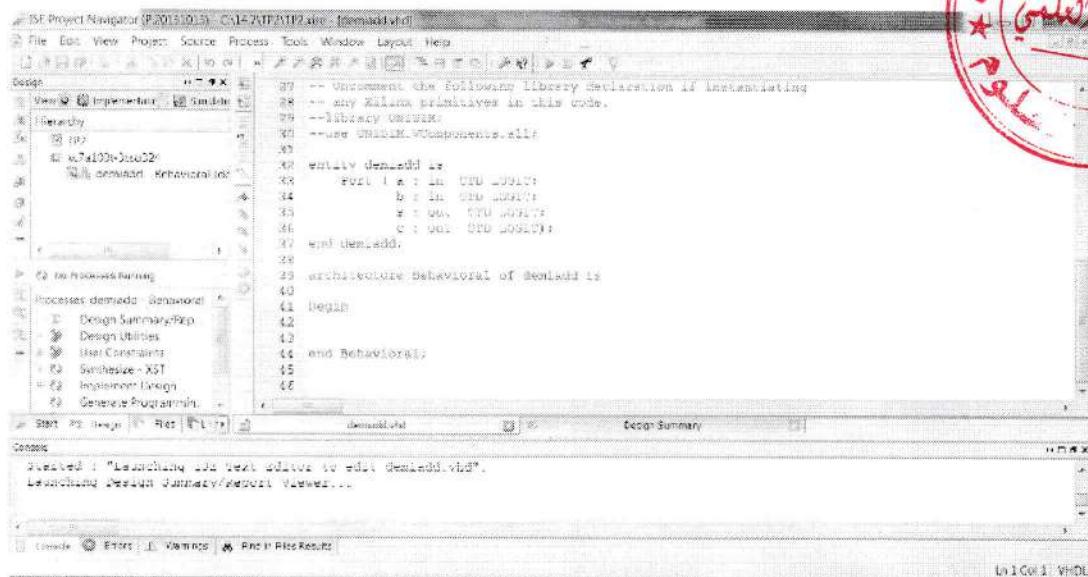

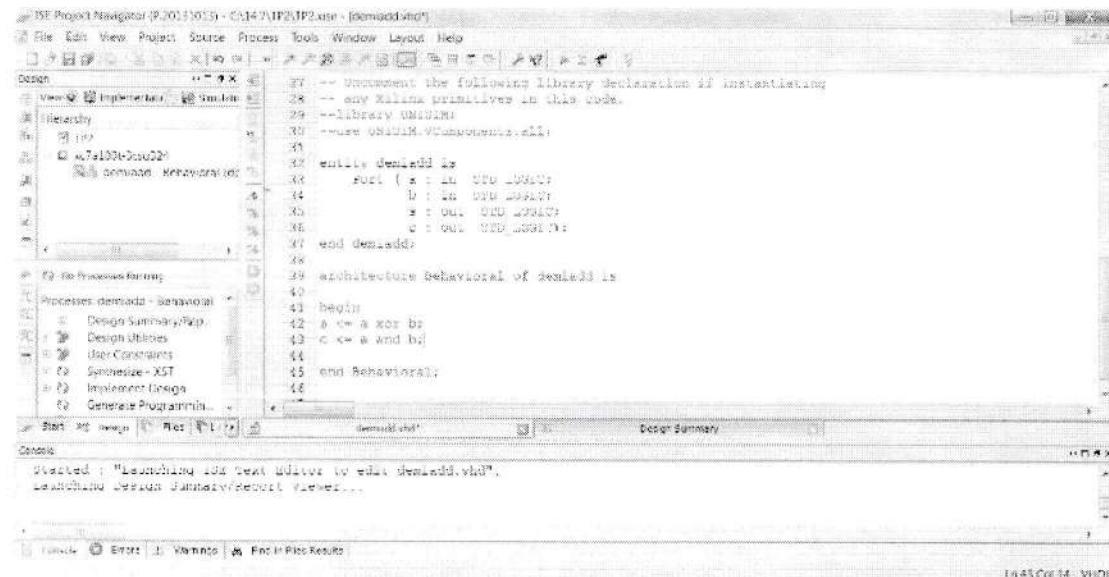

| Figure 109. Le fichier <b>demiadd.vhd</b> .....                                  | 133 |

| Figure 110. Le fichier <b>demiadd.vhd</b> est compléter .....                    | 134 |

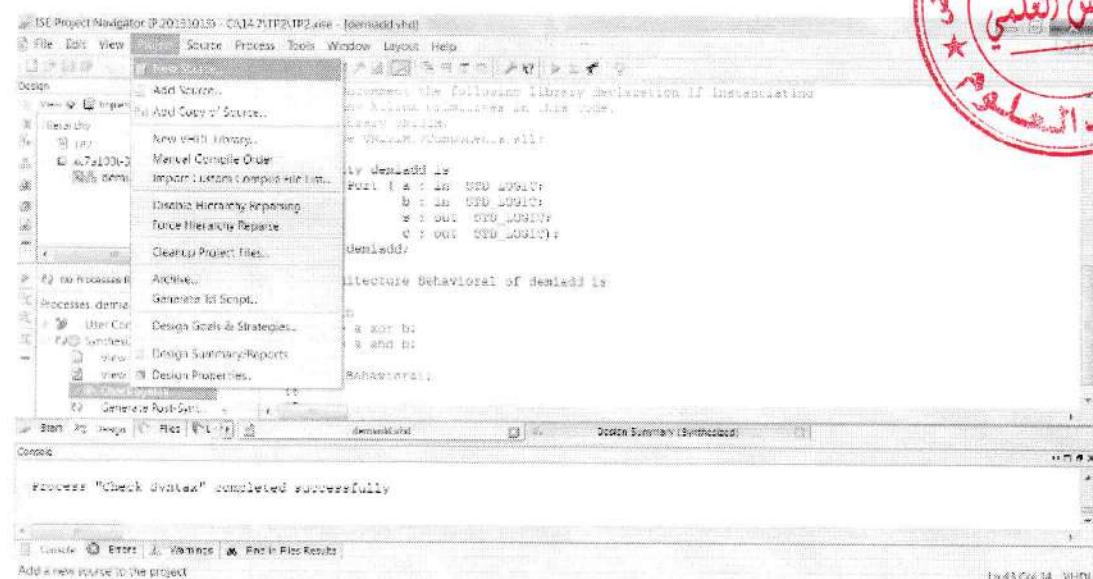

| Figure 111. La vérification du programme .....                                   | 135 |

| Figure 112. Exécution de <b>Check Syntax</b> .....                               | 135 |

| Figure 113. La création d'une autre source .....                                 | 136 |

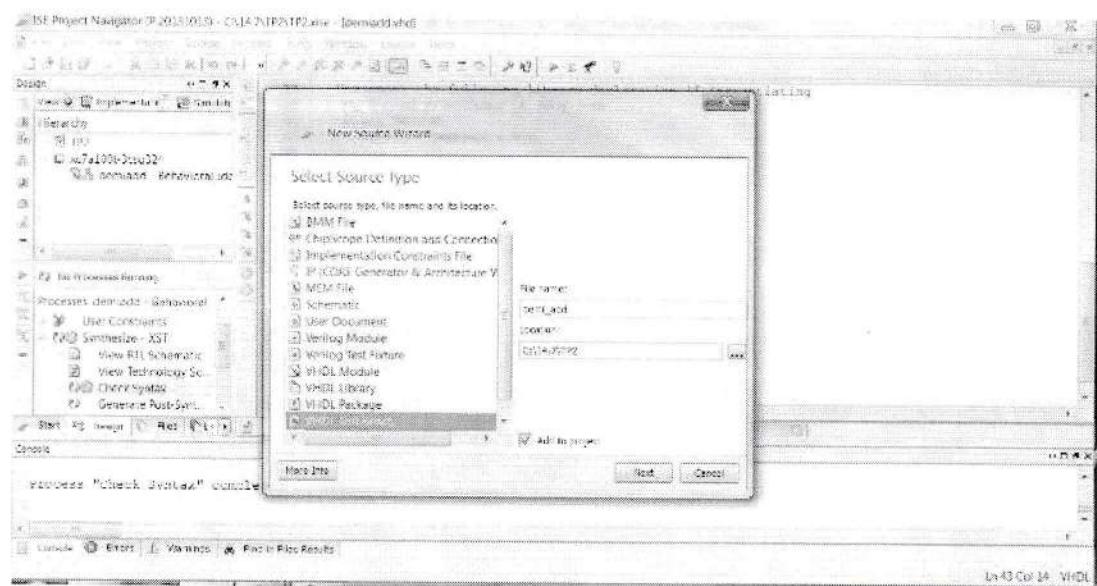

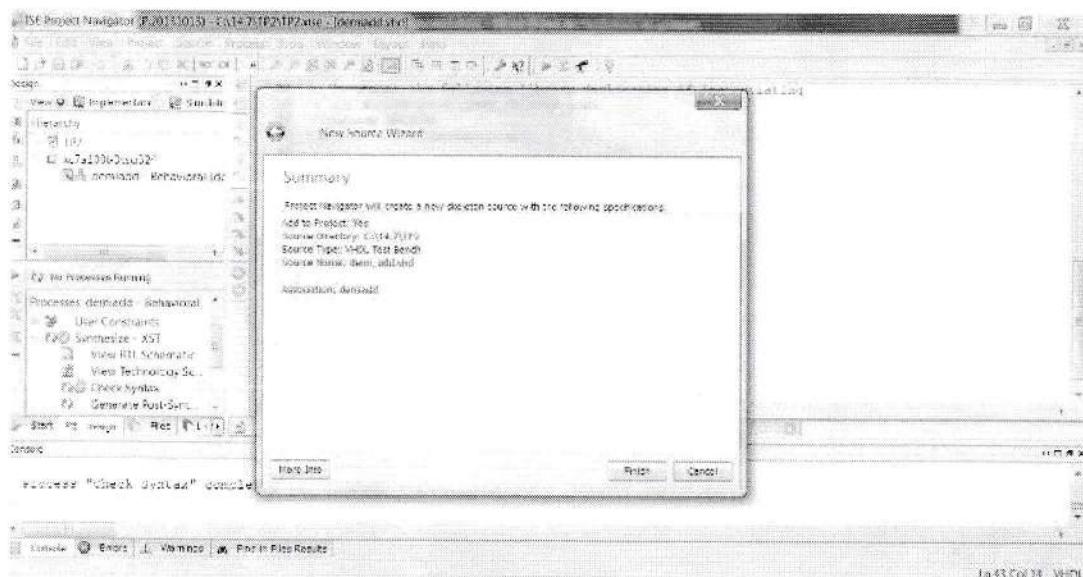

| Figure 114. Création du fichier <b>VHDL Test Bench</b> .....                     | 136 |

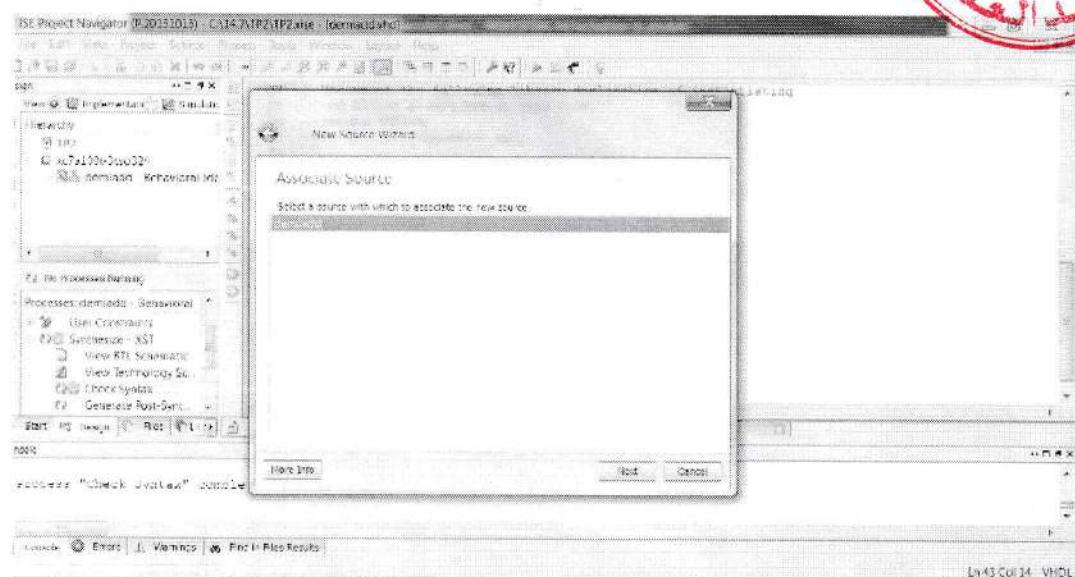

| Figure 115. Association des deux fichiers .....                                  | 137 |

| Figure 116. Récapitulation du fichier <b>demi_add.vhd</b> .....                  | 137 |

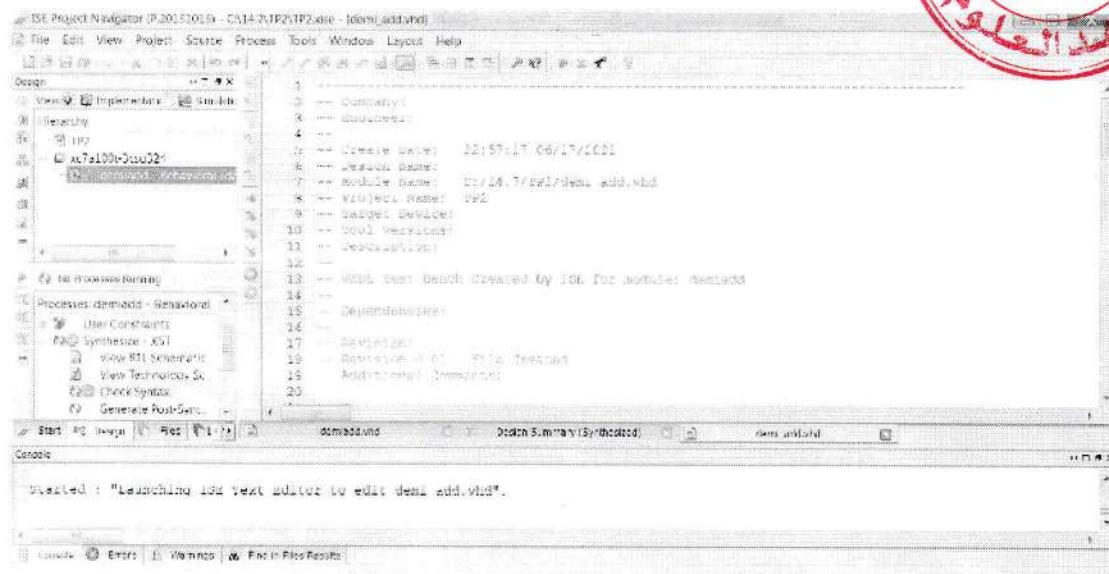

| Figure 117. Création du fichier <b>demi_add.vhd</b> .....                        | 138 |

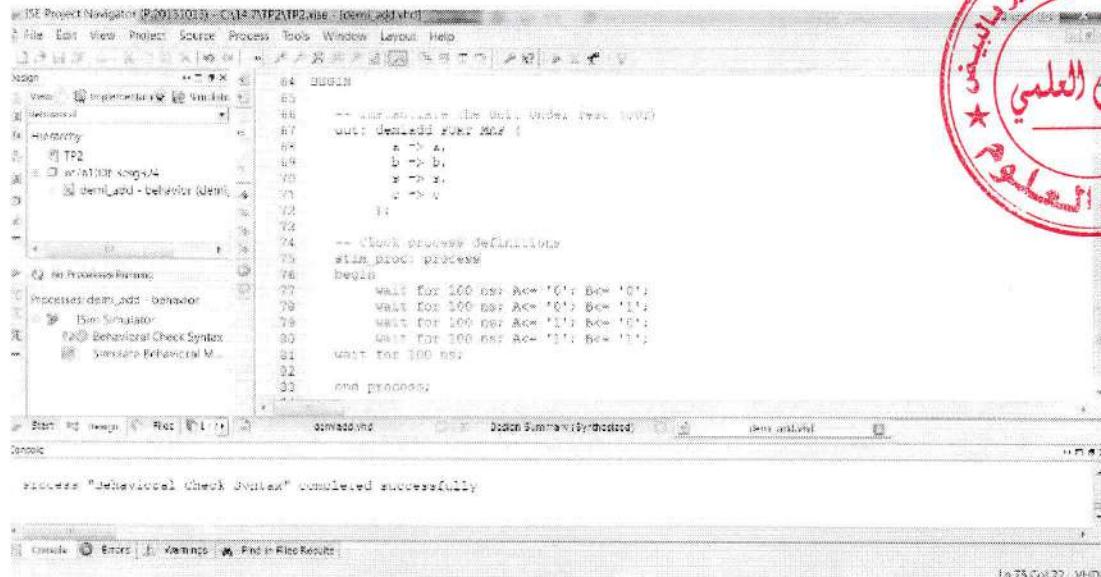

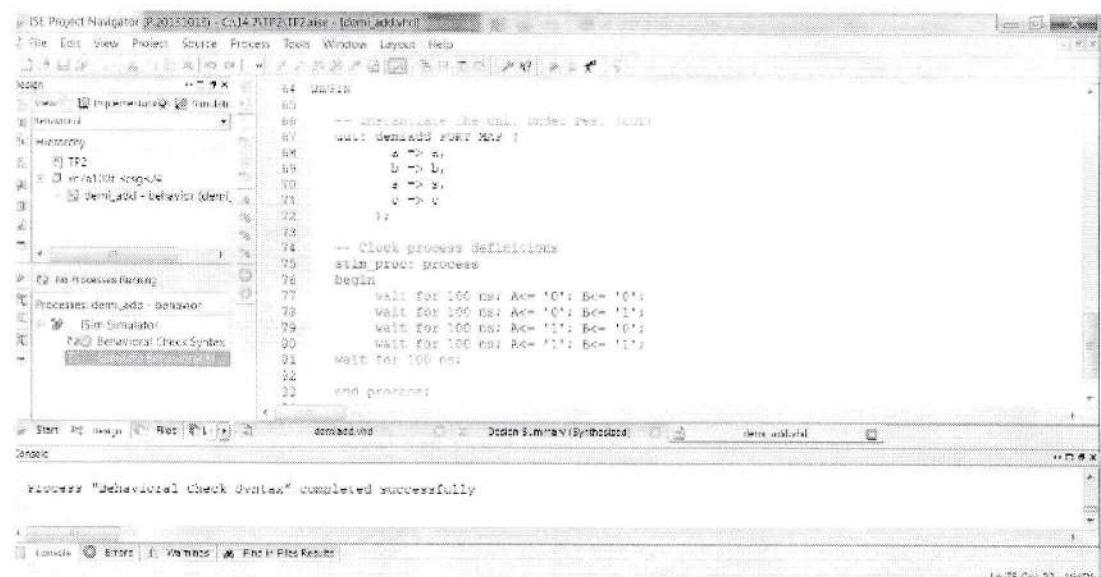

| Figure 118. Fichier <b>demi_add.vhd</b> programmé .....                          | 140 |

| Figure 119. Vérification <b>Behavioral Check Syntax</b> .....                    | 141 |

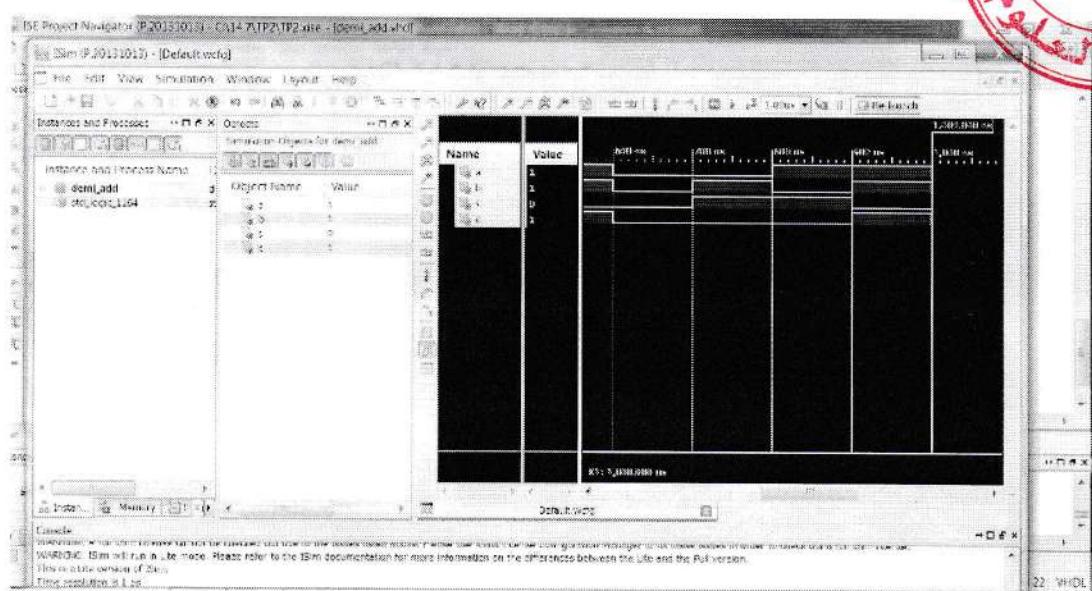

| Figure 120. Le model de simulation est compléter pour le demi additionneur ..... | 141 |

| Figure 121. Le chronogramme d'un demi-additionneur .....                         | 141 |

## Liste des tableaux :

|                                                           |     |

|-----------------------------------------------------------|-----|

| Table 1. Differentes familles PLD .....                   | 12  |

| Table 2. Différentes configurations.....                  | 29  |

| Table 3. Tableau comparative entre CPLD et FPGA .....     | 38  |

| Table 4. Criteres pour les interconnexions.....           | 46  |

| Table 5. Differents types d'operateur .....               | 91  |

| Table 6. Type de déclaration .....                        | 107 |

| Table 7. Signal et variable .....                         | 111 |

| Table 8. Le fichier <b>porteand.vhd</b> .....             | 119 |

| Table 9. Partie architecture .....                        | 120 |

| Table 10. Fichier <b>porte_and.vhd</b> .....              | 125 |

| Table 11. Le fichier <b>demiadd.vhd</b> (incomplet) ..... | 134 |

| Table 12. La partie du fichier est compléter.....         | 134 |

| Table 13. Le fichier <b>demi_add.vhd</b> .....            | 140 |

## Introduction :

Les conceptions électroniques numériques continuent d'évoluer vers des composants plus complexes et à plus grand nombre de broches fonctionnant à des fréquences d'horloge plus élevées, cela rend considérablement plus difficile la conception des cartes de prototypage et débogage dans un laboratoire avec un analyseur logique et un oscilloscope. Cela est dû au fait que les signaux sont de plus en plus difficiles à sonder physiquement et parce que leur sondage est plus susceptible de modifier le fonctionnement du circuit.

Aujourd'hui une grande partie de l'électronique numérique (logique combinatoire et séquentiel), personnalisée est conçue dans des ASIC (Application Specific Integrated Circuit, *Circuit intégré spécifique à l'application*) ou des FPGA (Field Programmable Gate Array, *Réseau de portes programmables*) avec les dispositifs VHDL (Hardware Description Language, *langage de description matérielle*) et FPGA permettent aux concepteurs de développer et de simuler rapidement un circuit numérique sophistiqué, de le réaliser sur un dispositif de prototypage et de vérifier le fonctionnement de l'implémentation physique. Au fur et à mesure que ces technologies mûrissent, elles sont devenues une pratique courante. Nous pouvons désormais utiliser un PC et une carte de prototypage FPGA peu coûteuse pour construire un système numérique complexe et sophistiqué.

Ce polycopié est destiné aux étudiants de la première année master électronique (système embarqué) les étudiants auront à étudier les différents types de circuits programmables, ainsi que les différentes méthodes de conception en particulier la programmation en utilisant les langages de description matérielle.

## Chapitre 1 : Les Réseaux Logiques Programmables (PLD)

---

## 1.1 Introduction

Il y a quelques années la réalisation d'un montage en électronique numérique impliquait l'utilisation d'un nombre important de circuits intégrés logiques. Ceci avait pour conséquences un prix de revient élevé, une mise en œuvre complexe et un circuit imprimé de taille importante. Le développement des mémoires utilisées en informatique fut à l'origine des premiers circuits logiques programmables (PLD : Programmable Logic Device). Ces structures (logique programme) ont besoin de s'interfacer entre elles. Elles utilisent généralement pour réaliser ces interfaces des fonctions à base de fonctions logiques élémentaires, compteurs, registres. Le nombre de circuits nécessaires pour remplir ces fonctions peut devenir très vite important. Les fonctions logiques programmables sont des circuits disposant des entrées et des sorties dont l'utilisateur peut programmer le schéma logique d'après les besoins liées à la fonction souhaitée : Logique combinatoire et/ou séquentielle.

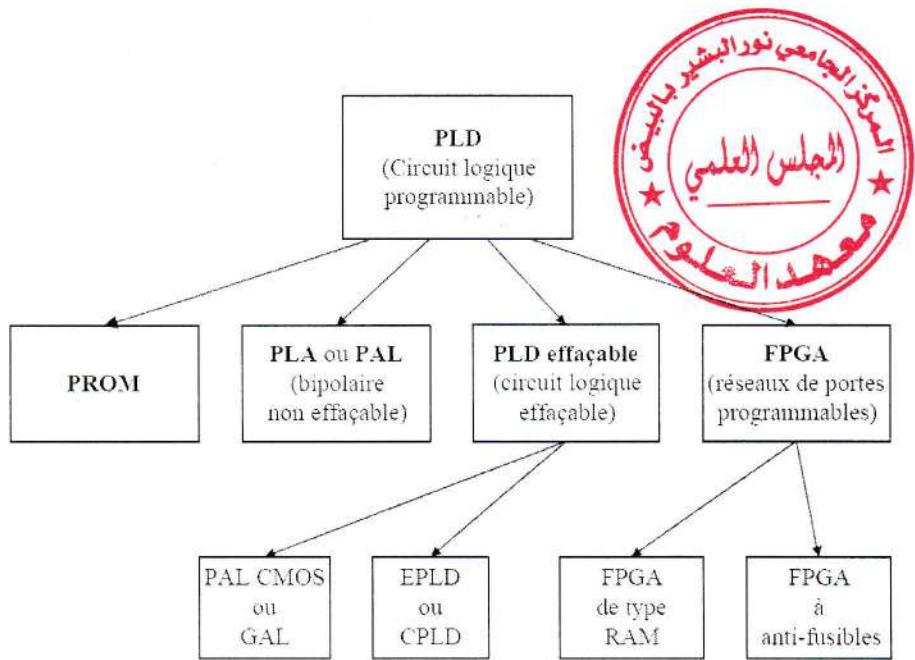

Ces composants sont appelés des PLD ce type de produit peut intégrer dans un seul circuit plusieurs fonctions logiques programmables par l'utilisateur. Les PLD sont utilisés pour remplacer l'association de plusieurs boîtiers logiques. Le câblage est simplifié, l'encombrement et le risque de pannes est réduit. Certains PLD ne permettent pas la relecture de la fonction logique programmée, c'est pratique lorsque le programme doit rester confidentiel. Ces circuits disposent d'un certain nombre de broches d'entrées et de sorties. L'utilisateur associe ces broches aux équations logiques (plus ou moins complexes) qu'il programme dans le circuit. Sa mise en œuvre se fait très facilement à l'aide d'un programmateur, d'un micro-ordinateur et d'un logiciel adapté. Rassemblés sous le terme générique PLD, les circuits programmables par l'utilisateur se décomposent en deux familles :

1. les PROM, les PLA, les PAL et les EPLD,

2. les FPGA.

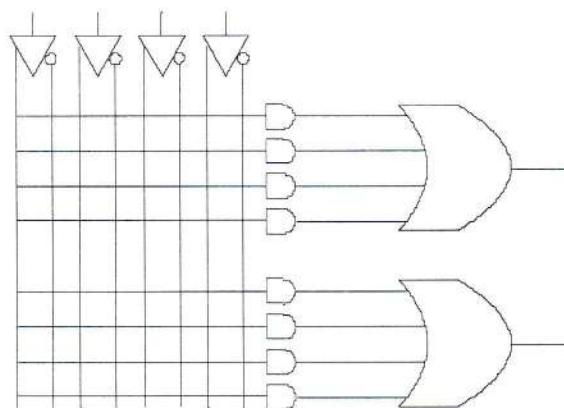

Figure 1. Structure des réseaux logiques combinatoires

### Structure des réseaux logiques combinatoires :

#### 1.2 Structure de base d'un PLD :

La plupart des PLDs suivent la structure suivante :

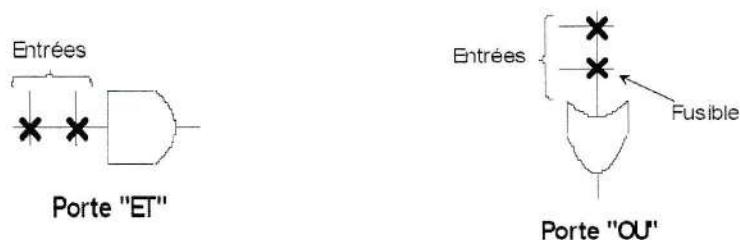

- Un ensemble d'opérateurs « ET » sur lesquels viennent se connecter les variables d'entrée et leurs compléments.

- Un ensemble d'opérateurs « OU » sur lesquels les sorties des opérateurs « ET » sont connectées.

- Une éventuelle structure de sortie (Portes in verseuses, logique 3 états, registres...). Les deux premiers ensembles forment chacun ce qu'on appelle une matrice les interconnexions de ces matrices doivent être programmables. C'est la raison pour laquelle elles sont assurées par des fusibles qui sont « grillés » lors de la programmation. Lorsqu'un PLD est vierge toutes les connexions sont assurées.

Figure 2. Symbolisation des portes logiques pour les PLD

### 1.3 Convention de notation :

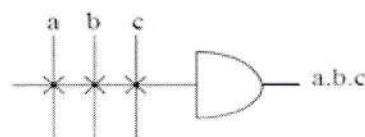

Afin de présenter des schémas clairs et précis, il est utile d'adopter une convention concernant les connexions à fusibles. Les deux figures suivantes représentent la fonction 3 entrées. La figure b) n'est qu'une version simplifiée du schéma de la figure a).

Figure 3. Symbole d'une porte AND à 3 entrées

Figure 4. Symbole simplifié d'une porte AND

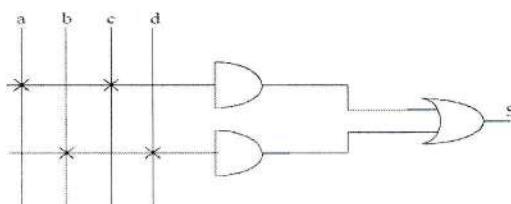

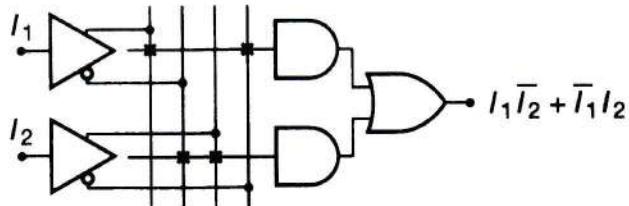

Un exemple de notation est donné sur la figure ci-contre. La fonction réalisée est  $S = (a \cdot c) + (b \cdot d)$ . Une croix, à une intersection, indique la présence d'une connexion à fusible non claqué. L'absence de croix signifie que le fusible est claqué. La liaison entre la ligne horizontale et verticale est rompue. La sortie S réalise une fonction OU des 2 termes produits  $(a \cdot c)$  et  $(b \cdot d)$ .

Figure 5. La sortie S réalise une fonction OU avec deux fonctions AND.

### 1.4 Représentation de l'architecture interne d'un PLD :

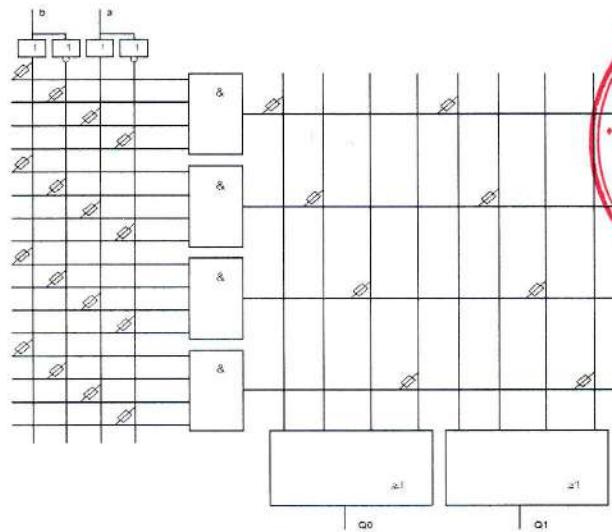

Un exemple de ce type de structure est présenté par la figure ci-dessous. On peut remarquer que la représentation d'une telle structure est complexe alors que le nombre de portes intégrées est peu important. Les constructeurs ont donc très rapidement adoptés un autre type de représentation rendant les schémas beaucoup plus lisibles. On remarquera que la norme adoptée est américaine. Un exemple de cette représentation est donné par la figure suivante :

Figure 6. Structure de base d'un PLD

Figure 7. Structure de base avec les normes des constructeurs

La figure 7 représente la structure interne d'un PLD ayant ses fusibles intacts. Les équations logiques de  $Q_0$  et  $Q_1$  sont :

$$Q_0 = Q_1 = \bar{a} \cdot \bar{b} \cdot a \cdot b + \bar{a} \cdot \bar{b} \cdot a \cdot b + \bar{a} \cdot \bar{b} \cdot a \cdot b + \bar{a} \cdot \bar{b} \cdot a \cdot b = 0.$$

Si on veut obtenir les fonctions suivantes :

$$Q_1 = \bar{a} \cdot \bar{b} + a \cdot b \text{ et } Q_2 = a \cdot \bar{b} + \bar{a} \cdot b$$

On « grillera » des fusibles de façon à obtenir le schéma suivant de la figure 8 :

**x** : Fusible intact

Figure 8. Structure après programmation

Les premiers circuits programmables apparus sur le marché sont les PROM bipolaires à fusibles. Cette mémoire est l'association d'un réseau de ET fixes, réalisant le décodage d'adresse, et d'un réseau de OU programmables, réalisant le plan mémoire proprement dit. On peut facilement comprendre que, outre le stockage de données qui est sa fonction première, cette mémoire puisse être utilisée en tant que circuit logique. La figure ci-dessous représente la structure logique d'une PROM bipolaire à fusibles.

*Figure 9. Structure logique d'une PROM bipolaire à fusibles*

Chaque sortie  $O_i$  peut réaliser une fonction OU de 16 termes produits de certaines combinaisons des 4 variables A, B, C et D. Avec les PROM, les fonctions logiques programmées sont spécifiées par les tables de vérités. Le temps de propagation est indépendant de la fonction implantée.

### 1.5 Les différentes familles de PLD :

Il existe plusieurs familles de PLD qui sont différenciées par leur structure interne. Le tableau suivant présente certaines de ces familles.

| Type | Nombres de portes intégrées | Matrice ET   | Matrice OU   | Effaçable      |

|------|-----------------------------|--------------|--------------|----------------|

| PROM | 2000 à 500000               | Fixe         | Programmable | Non            |

| PAL  | 10 à 100                    | Programmable | Fixe         | Non            |

| PLA  | 10 à 100                    | Programmable | Programmable | Non            |

| GAL  | 10 à 100                    | Programmable | Fixe         | Électriquement |

| EPLD | 100 à 3000                  | Programmable | Fixe         | Aux UV         |

| FPGA | 2000 à 3000                 | Programmable | Programmable | Électriquement |

Table 1. Différentes familles PLD

### 1.6 PROM

Certaines de ces familles possèdent en plus des matrices « ET » et « OU », de la logique séquentielle (Bascules « D », « JK »...) placée après les entrées ou avant les sorties du PLD.

Les « PROMs » sont des circuits utilisés en informatique pour mémoriser de façon définitive des données : ce sont des « Mémoires mortes ». Il existe des versions effaçables comme les UV PROM (aux U-V) et les EEPROM (électriquement).

### 1.7 Les PLA

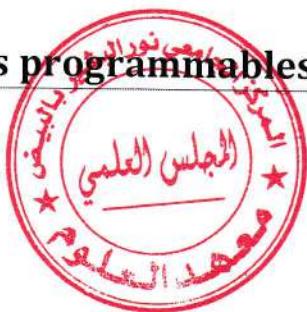

L'un des premiers PLD commerciaux mis au point à l'aide de la technologie moderne des circuits intégrés était le réseau logique programmable (PLA). En 1970, Texas Instrument a introduit le PLA avec une architecture prenant en charge la mise en œuvre d'expressions logiques arbitraires, somme de produits. Le PLA a été fabriqué avec un réseau dense de portes ET, appelé un plan ET, et un réseau dense de portes OU, appelé un plan OR. Les entrées du PLA avaient chacune un inverseur afin de fournir la variable d'origine et son complément. Des expressions logiques SOP (sum of products, *somme de produit*) arbitraires pourraient être implémentées en créant des connexions entre les entrées, le plan ET et le plan OU. Les PLA d'origine ont été fabriqués avec toutes les caractéristiques nécessaires, à l'exception des connexions finales pour implémenter les fonctions SOP. Lorsqu'un client a fourni l'expression SOP souhaitée, les connexions ont été ajoutées comme étape finale de la fabrication. Cette technique de configuration était similaire à une approche MROM. Un schéma plus compact pour le PLA est dessiné en représentant toutes les entrées dans le ET et OU portes avec un seul fil. Les connexions sont indiquées en insérant des X aux intersections des fils.

La Figure 10 montre ce schéma PLA simplifié mettant en œuvre deux expressions logiques SOP différentes. Le concept du PLA (Programmable Logic Array) a été développé il y a plus de 20 ans. Il reprend la technique des fusibles des PROM bipolaires. La programmation consiste à faire sauter les fusibles pour réaliser la fonction logique de son choix. La structure des PLA est une évolution des PROM bipolaires. Elle est constituée d'un réseau de ET programmables et d'un réseau de OU programmables. Sa structure logique est la suivante :

*Figure 10. Structure logique d'un PLA*

Chaque sortie  $O_i$  peut réaliser une fonction OU de 16 termes produits des 4 variables A, B, C et D. Avec cette structure, on peut implémenter n'importe quelle fonction logique combinatoire. Ces circuits sont évidemment très souples d'emploi, mais ils sont plus difficiles à utiliser que les PROM. Statistiquement, il s'avère inutile d'avoir autant de possibilité de programmation, d'autant que les fusibles prennent beaucoup de place sur le silicium. Ce type de circuit n'a pas réussi à pénétrer le marché des circuits programmables. La demande s'est plutôt orientée vers les circuits PAL.

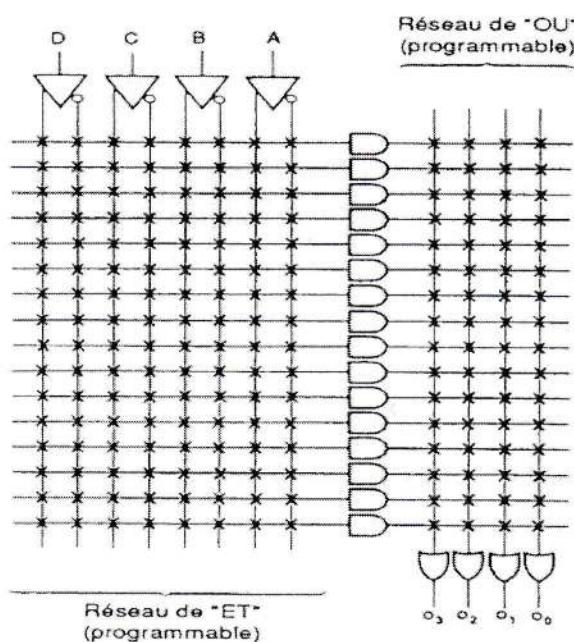

## 1.8 Les PAL :

L'un des inconvénients du PLA original était que la programmabilité du plan OU provoquait des retards de propagation importants à travers les circuits logique combinatoire. Afin d'améliorer les performances des PLA, la logique de matrice programmable (PAL) a été introduite en 1978 par la société Monolithic Memories, Inc. Le PAL contenait un plan ET programmable et un plan OU fixe. Le plan OR fixe a amélioré les performances de cette architecture programmable. Bien que le fait de ne pas avoir de plan OU programmable réduise la flexibilité de l'appareil, la plupart des expressions SOP pourraient être manipulées pour fonctionner avec un PAL. Une autre contribution du PAL était que le plan AND pouvait être programmé à l'aide de fusibles. Au départ, toutes les connexions étaient présentes dans le plan AND. Un programmeur externe a été utilisé pour faire sauter les fusibles afin de déconnecter les entrées des portes ET. Alors que l'approche par fusible fournissait une programmation unique, la possibilité de configurer la post-fabrication logique était une avancée significative par rapport au PLA, qui devait être programmé chez le fabricant.

Les PALs sont les circuits logiques programmables les plus anciens à être utilisés pour réaliser des fonctions logiques ». Un composant logique programmable PAL est basé sur le concept qu'il est possible de remmener toute équation logique en une somme de produits. La programmation s'effectue par destruction de fusible (un fusible détruit équivaut à un circuit ouvert), ils ne sont donc programmables qu'une fois, ce qui peut être gênant en phase de développement. Un PAL permet de remplacer jusqu'à 10 boîtiers SSI ou 2 à 3 boîtiers MSI.

#### **1.8.1 Principe d'un PAL :**

Ce PAL simplifié comporte 2 entrées  $I_1$  et  $I_2$  et une sortie O. Huit fusibles ( $F_1$  à  $F_8$ ) permettent de réaliser diverses fonctions logiques. La programmation va consister à faire sauter les fusibles nécessaires afin de réaliser la fonction voulue. La programmation va constituer à détruire les fusibles pour obtenir les fonctions désirées, en sachant que lors de l'achat d'un P.A.L tous les fusibles sont vierges ou pas détruits.

Figure 12. Symbole simplifié d'un PAL

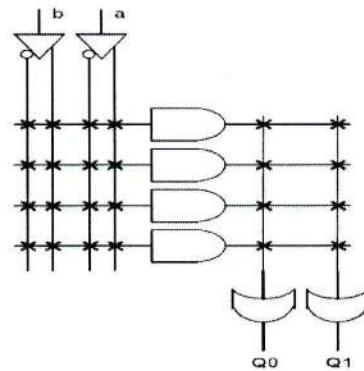

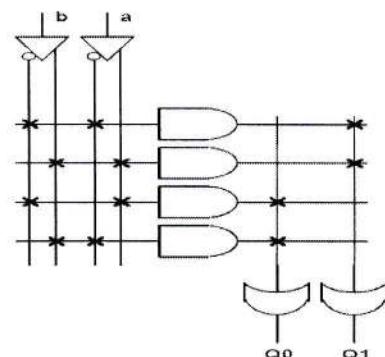

### 1.8.2 Convention de représentation :

La représentation simplifiée ne montre pas tous les fusibles, les entrées de la porte ET sont regroupées sur une seule ligne. Une croix représente un fusible intact.

#### Exemple de programmation d'un PAL :

Figure 13. Exemple de programmation d'un PAL

On souhaite réaliser une fonction OU EXCLUSIF :  $O = I_1 \oplus I_2 = I_1\bar{I}_2 + \bar{I}_1I_2$

La

fusion des fusibles est obtenue en appliquant à leurs bornes une tension de 11,5 V pendant 10 à 50 µS (leur tension de fonctionnement est environ de 5V). Cette opération est bien sûr effectuée en utilisant un programmeur adapté. La structure de base de ce PLD est présentée par le schéma suivant.

- Ils possèdent des matrices ET programmables, et des matrices OU fixes.

Figure 11. Structure simplifié d'un PAL

- La fusion des fusibles est obtenue en appliquant à leurs bornes une tension de 11.5V pendant 10 à 50 µS (leur tension de fonctionnement est de 5V).

- Cette opération est sûre effectuée en utilisant un programmeur adapté.

Figure 14. Structure de base d'un PAL

Figure 15. Porte à sortie 3 états

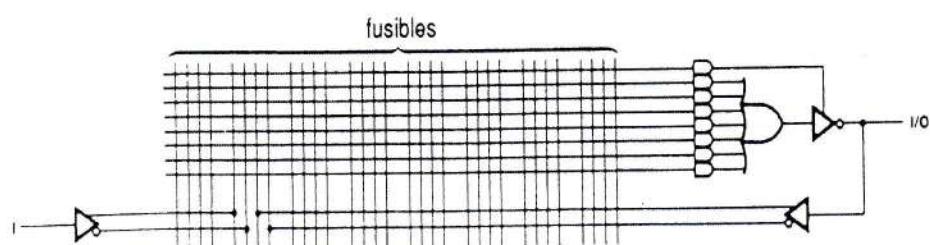

Porte à sortie 3 états, permettant de déconnecter la broche de la matrice "ET" (rendre indépendant) la sortie I/O de l'état logique imposé par la sortie du OU. Dans ce cas la sortie I/O est utilisée en entrée

Certaines broches de ces circuits peuvent être utilisées aussi bien en entrée qu'en sortie grâce à un système de logiques 3 états. La commande de cette dernière est configurée au

Figure 16. Structure logique d'un PAL

moment de la programmation. La structure de sortie permet aussi de réinjecter les sorties en entrée (Feed-back). Selon le type de PAL la structure de sortie peut être constituée d'une porte « NON », d'une porte « OU » Exclusive, d'une bascule « D » ou d'une combinaison des trois. Le nombre d'entrées et de sorties est lui aussi lié à la référence du PAL. La technologie employée est la même que pour les PLA. La figure qui suit représente la structure logique d'un PAL où chaque sortie intègre 4 termes produits de 4 variables. L'architecture du PAL a été conçue à partir d'observations indiquant qu'une grande partie des fonctions logiques ne requiert que quelques termes produits par sortie. L'avantage de cette architecture est l'augmentation de la vitesse par rapport aux PLA. En effet, comme le nombre de connexions est diminué, la longueur des lignes d'interconnexion est réduite. Le temps de propagation entre une entrée et une sortie est par conséquent réduit.

Le PAL possède toujours des entrées simples sur le réseau de ET programmables, mais aussi des broches spéciales qui peuvent être programmées :

- en entrée simple en faisant passer le buffer de sortie trois états en haute impédance,

- en sortie réinjectée sur le réseau de ET. Cela permet d'augmenter le nombre de termes produits disponibles sur les autres sorties.

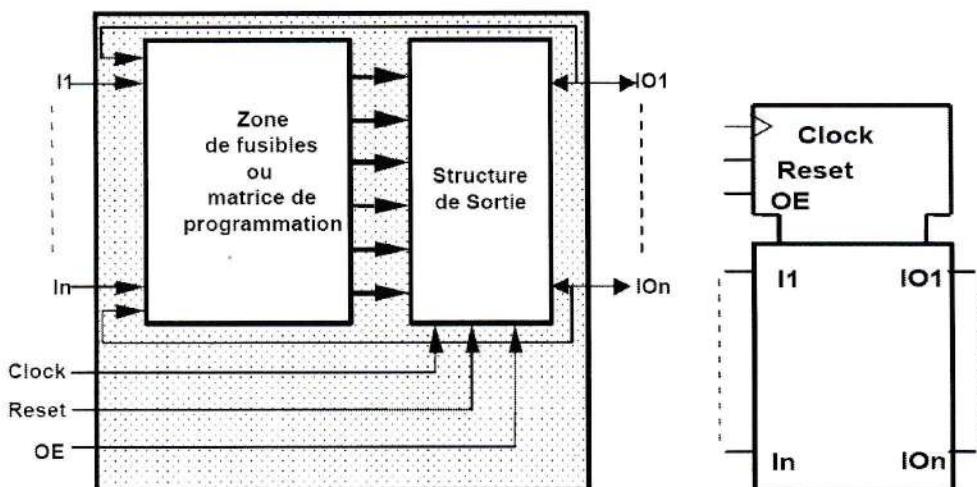

### 1.8.3 Les différentes structures :

Structure générale :

Tout P.A.L est constitué :

- D'entrées (Input) :  $I_1$  à  $I_n$  avec  $8 < n < 20$ .

- De sorties (Output) Ou d'entrées / sorties (I/O) de type Totem Pôle ou Trois Etats :  $01$  à  $On$  ou  $IO_1$  à  $IO_n$  ( $2 < n < 15$ ).

On peut trouver aussi :

- Une entrée d'horloge (Clock) : Clk ou Clock.

- Une entrée de validation des sorties trois états : OE (Output Enable) ou Enable.

- Une entrée de remise à zéro des registres : RESET.

D'un point de vue fonctionnel un P.A.L. est constitué d'une zone d'entrée de fusibles ou matrice de programmation et une structure de sortie non programmable déterminant le type de circuit voir schéma ci-dessous.

#### Structure et symbolisation normalisée :

Figure 17. Schéma synoptique d'un PAL

**Remarque :** Sur un schéma comportant un PAL, on doit écrire les équations qui relient les entrées aux sorties ou le nom du document contenant les équations du P.A.L.

La programmation de ces circuits s'effectue par destruction de fusibles. Une fois programmée on ne peut plus les effacer. On distingue deux sous familles :

- Les P.A.L. combinatoires ou P.A.L. simples. Ils sont constitués de fonctions de logique combinatoire.

- Les P.A.L. à registres ou F.P.L.S. Field Programmable Logic Séquenceur pour séquenceur logique programmable. Ils sont constitués de logique combinatoire et séquentielle (Registre).

Il existe un grand nombre de P.A.L utilisant des structures de sorties différentes. On peut distinguer trois types de structures de base :

- Combinatoire.

- Séquentielle.

- Versatile.

#### **1.8.4 Les différents types d'entrées /sorties :**

On distingue 3 principes utilisés pour les sorties. Selon le modèle, un ou plusieurs types de sorties peuvent être utilisés sur un même PAL.

##### **1.8.4.1 Entrées/Sorties combinatoires :**

Ces sorties 3 états sont rebouclées vers la matrice de fusibles. Une sortie peut donc servir de variable intermédiaire. En mode haute impédance (la sortie étant inhibée), on peut utiliser une broche de sortie comme étant une entrée. On parle alors d'entrée / sortie (I/O). Il existe trois types :

- H : (High) Porte ET suivit d'une Porte OU. Sortie active à l'état haut.

- L : (Low) Porte ET suivit d'une Porte NON OU. Sortie active à l'état bas.

Figure 18. PAL16L8

- C : (Combinée) programmable en type H ou L.

Figure 19. PAL combiné

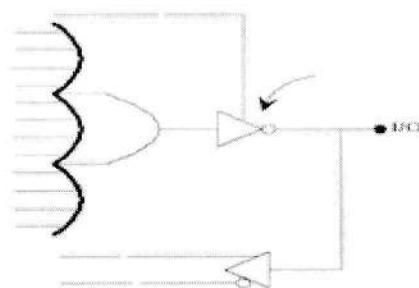

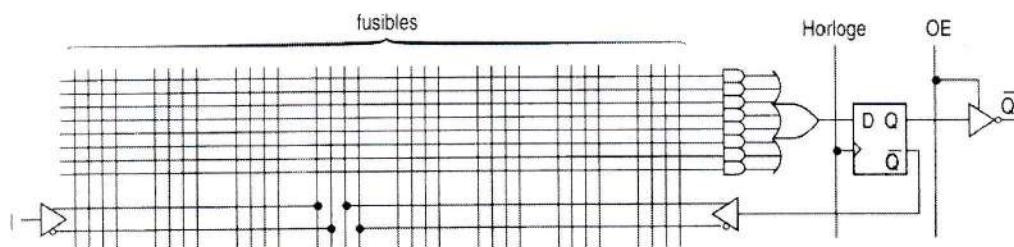

#### 1.8.4.2 Séquentielle :

Les architectures des PAL ont évolué vers les PAL à registres. Dans ces PAL, la sortie du réseau de fusibles aboutit sur l'entrée d'une bascule D. Ces sorties utilisent une bascule D qui permet la logique séquentielle. Par contre, une sortie à registre ne peut pas être utilisée comme entrée. La sortie Q peut aller vers une sortie, la sortie  $\bar{Q}$  étant reinjectée sur le réseau via un inverseur/non inverseur.

Il existe trois types :

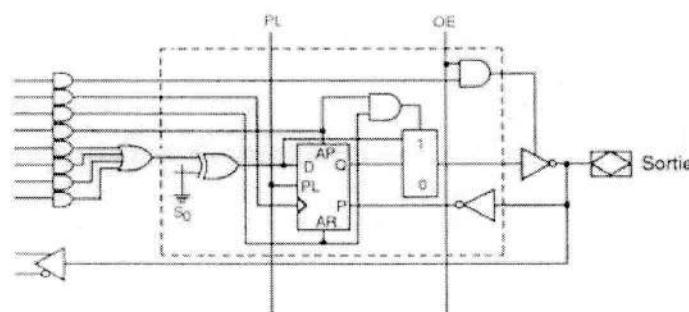

##### 1.8.4.2.1 Sorties à registres PAL de type R

Ces circuits sont composés de bascule D. Les sorties des bascules sont de type trois états contrôlées par un signal de validation Enable ou OE, et une horloge est commune à toutes les bascules (clock).

Figure 20. PAL type R

Figure 21.PAL16R6

#### 1.8.4.2.2 Sorties à Ou Exclusif et Registre PAL de type X

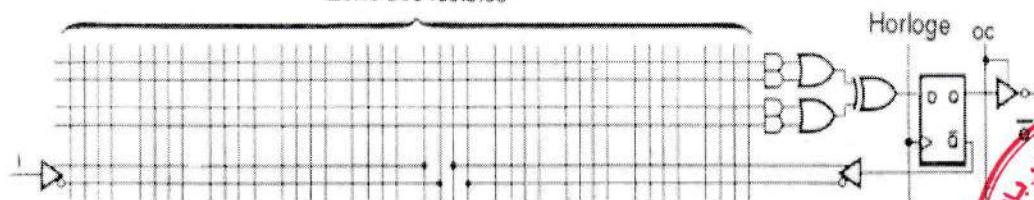

Zone des fusibles

Figure 22. PAL type X

#### 1.8.4.2.3 Sorties à Registre asynchrone PAL de type RA

Figure 23. PAL type RA

Les structures de sorties sont beaucoup plus évoluées par rapport aux autres P.A.L., elles se rapprochent des P.A.L. de type versatile.

Elles peuvent prendre quatre configurations suivant les valeurs de AP et AR.

Figure 24. Différentes configurations

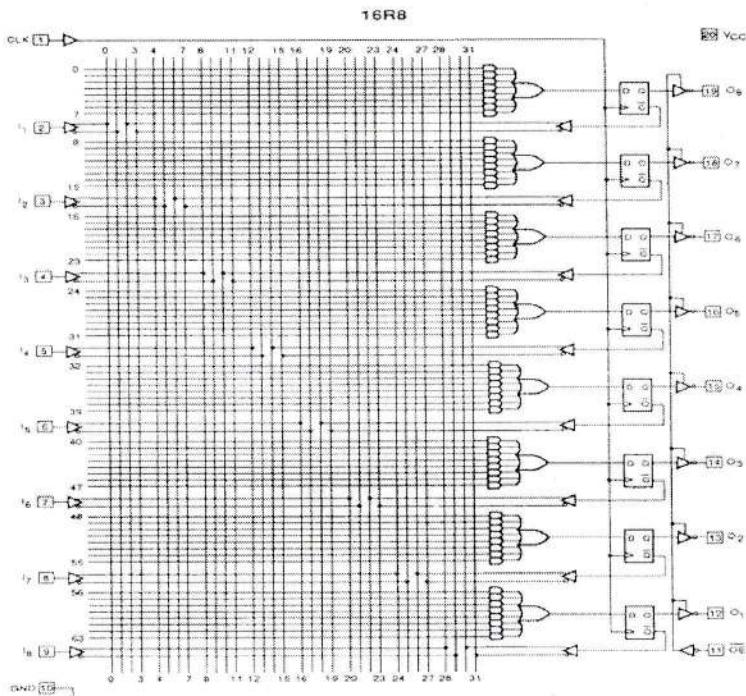

Avec cette structure, la sortie ne peut être utilisée comme entrée sur le réseau. L'exemple d'un PAL à registres 16R8 est donné. Il implémente 8 termes produits de 16 variables par sortie.

Figure 25. PAL à registre 16R8

D'après la notation employée par les fabricants, la référence 16R8 signifie :

- 16 : Nombre d'entrées au niveau du réseau de ET.

- R : PAL à registres.

- 8 : Nombre de sorties.

Les plus gros PAL standards sont les 20R8 et 20L8.

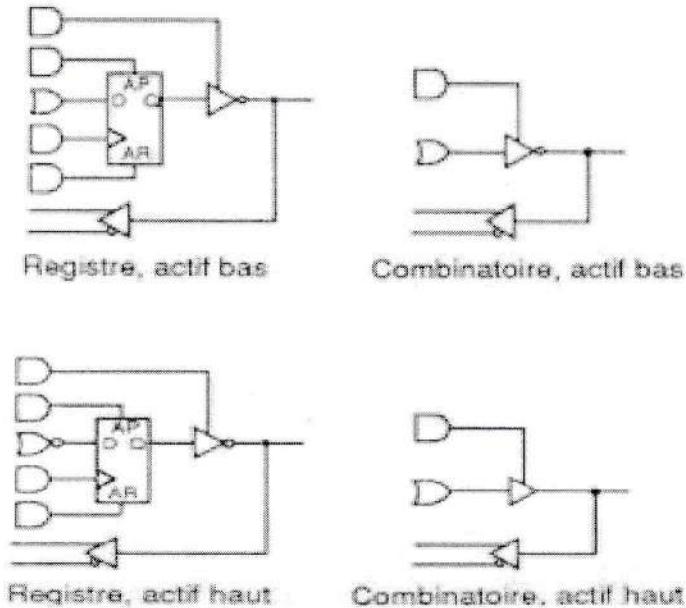

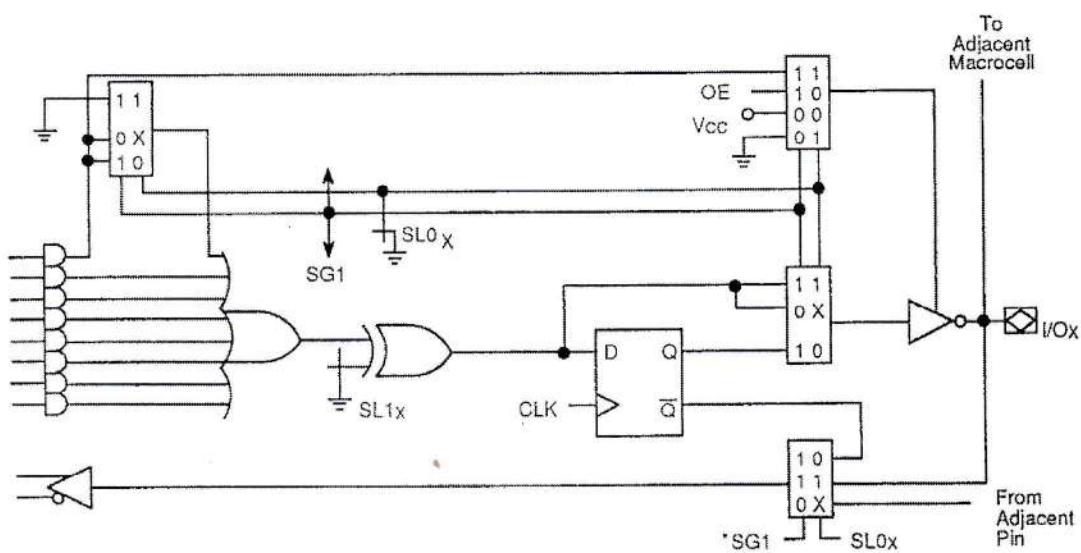

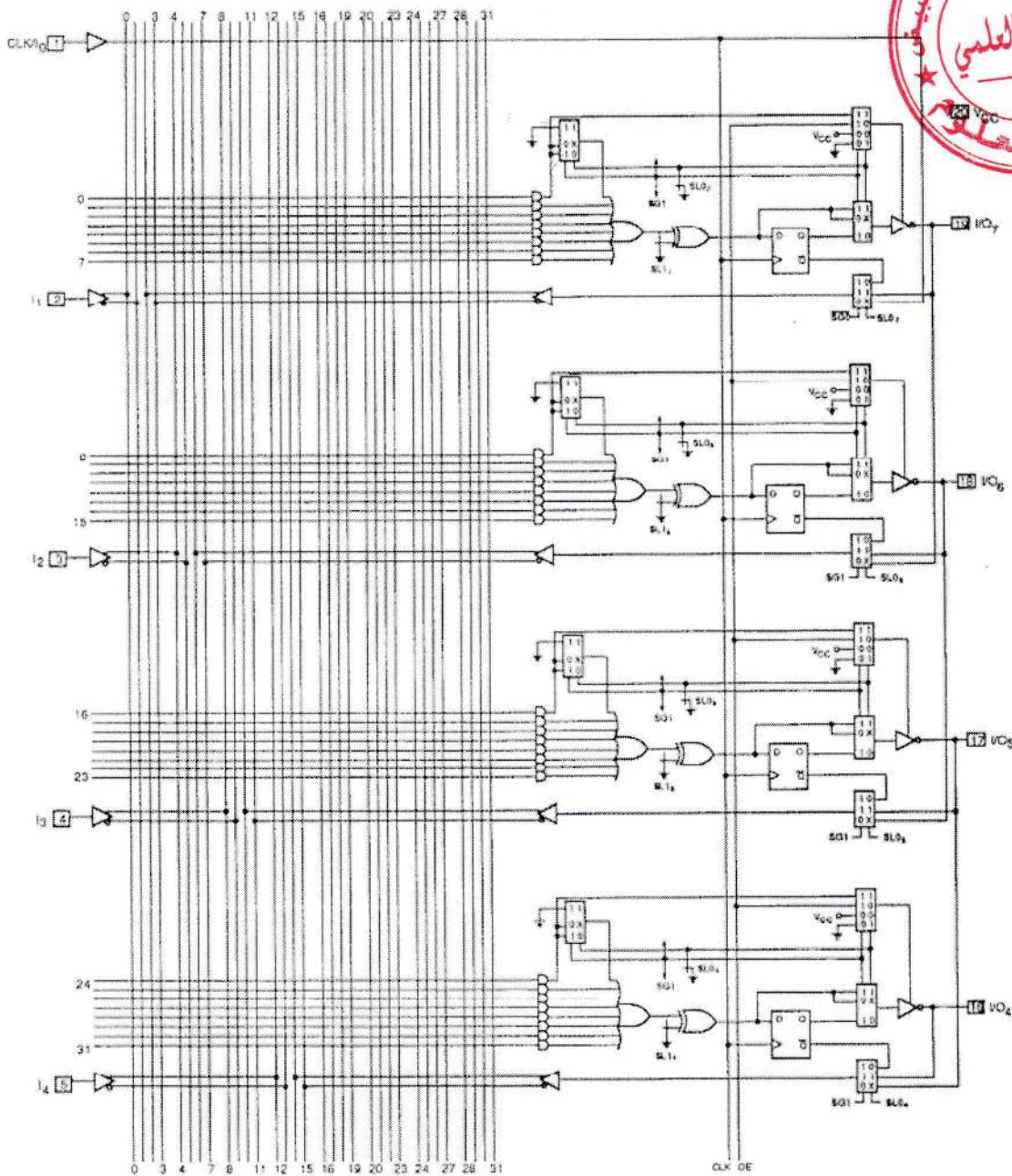

#### 1.8.4.3 Sorties versatiles PAL de type V

##### MODE D'EMPLOI

Le PALCE16V8 est un appareil PAL universel. Il en a huit macrocellules configurables indépendamment ( $MC_0$ - $MC_7$ ). Chaque macrocellule peut être configurée comme sortie enregistrée, sortie combinatoire, E / S combinatoires ou entrée dédiée. La matrice de programmation implémente un tableau logique ET programmable, qui pilote un tableau logique OU fixe. Les tampons pour les entrées de périphérique ont des sorties complémentaires pour fournir une polarité de signal d'entrée programmable par l'utilisateur. Les broches 1 et 11 servent respectivement d'entrées de tableau ou

d'activation d'horloge (CLK) et de sortie (OE) pour toutes les bascules. Les broches d'entrée inutilisées doivent être directement liées à Vcc ou GND. Les termes de produit avec tous les bits non programmés (déconnectés) supposent l'état HAUT logique et les termes de produit avec à la fois vrai et complément de tout signal d'entrée connecté prennent un état logique BAS. Les fonctions programmables du PALCE16V8 sont automatiquement configurées à partir des spécifications de conception de l'utilisateur, qui peuvent être dans un certain nombre de formats. La spécification de conception est traitée par le logiciel de développement pour vérifier la conception et créer un fichier de programmation. Ce fichier, une fois téléchargé sur un programmeur, configure l'appareil en fonction de la fonction souhaitée par l'utilisateur. L'utilisateur dispose de deux options de conception avec le PALCE16V8. Premièrement, il peut être programmé comme un périphérique PAL standard des séries PAL16R8 et PAL10H8. Le fabricant du programmeur PAL fournira les codes de périphérique pour les architectures de périphérique PAL standard à utiliser avec le PALCE16V8. Le programmeur programmera le PALCE16V8 dans l'architecture correspondante. Cela permet à l'utilisateur d'utiliser les fichiers JEDEC de périphérique PAL standard existants sans y apporter de modifications. Alternative, l'appareil peut être programmé comme PALCE16V8, où l'utilisateur doit utiliser le PALCE16V8 code de l'appareil. Cette option permet d'utiliser pleinement la macrocellule.

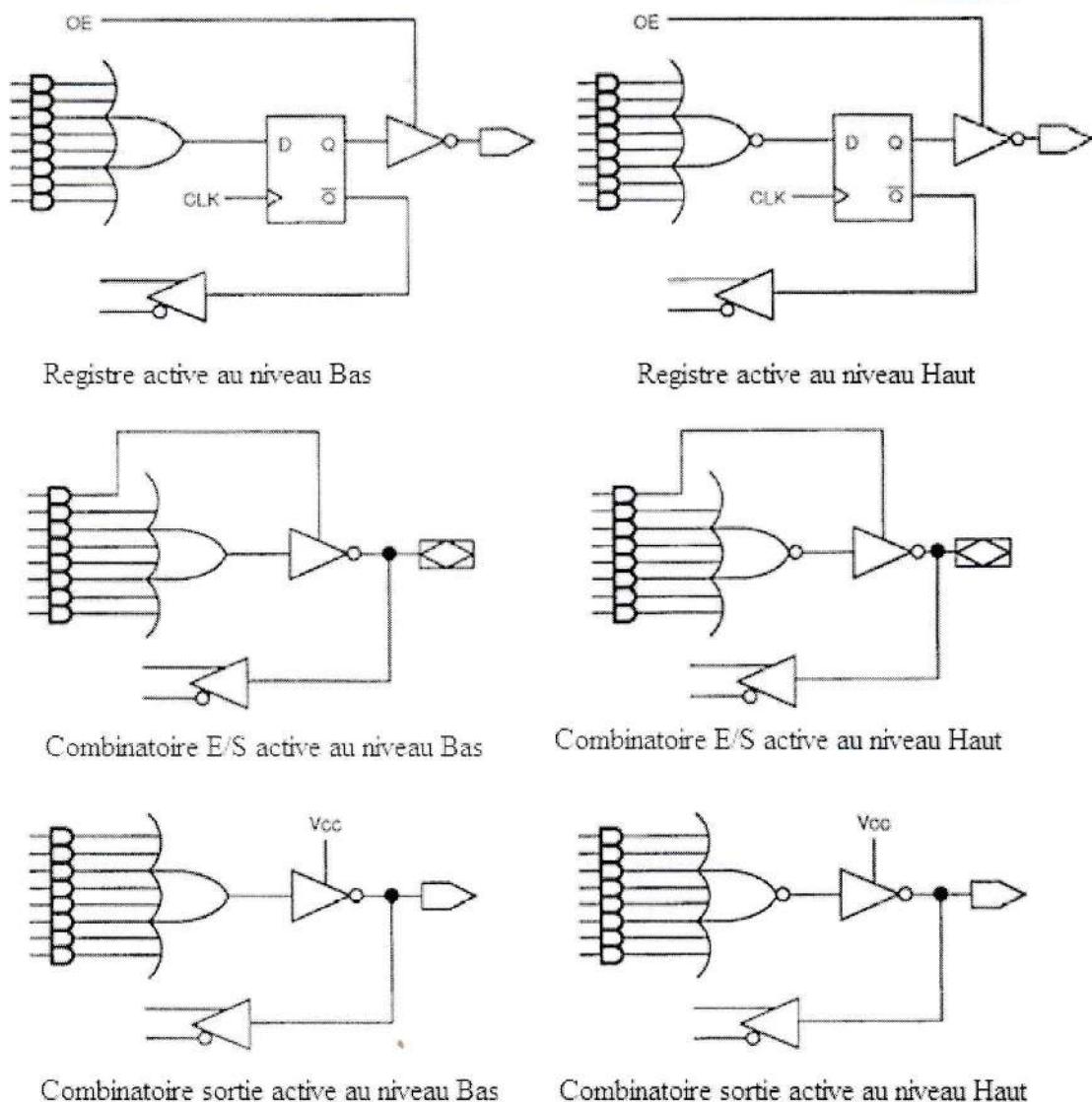

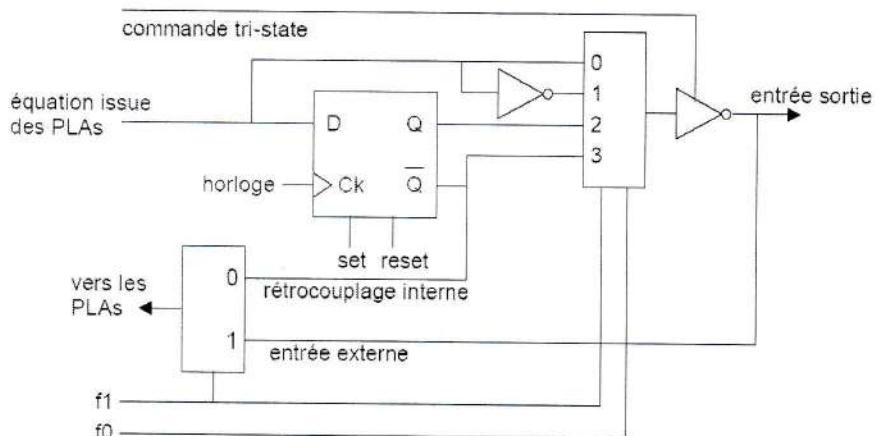

### Options de configuration

Chaque macrocellule peut être configurée comme l'une des suivantes : sortie enregistrée, sortie combinatoire, E / S combinatoire ou entrée dédiée. Dans la configuration de sortie enregistrée, le tampon de sortie est activé par la broche OE. Dans la configuration combinatoire, le tampon est soit contrôlé par un terme de produit, soit toujours activé. Dans la configuration d'entrée dédiée, il est toujours désactivé. Avec à l'exception de MC<sub>0</sub> et MC<sub>7</sub>, une macrocellule configurée comme une entrée dédiée dérive le signal d'entrée d'une E / S adjacente. MC<sub>0</sub> dérive son entrée de la broche 11 (OE) et MC<sub>7</sub> de la broche 1 (CLK). Les configurations des macrocellules sont contrôlées par le mot de contrôle de configuration. Il contient 2 bits globaux (SG0 et SG1) et 16 bits locaux (SLO<sub>0</sub> à SLO<sub>7</sub> et SL1<sub>0</sub> à SU<sub>7</sub>). SG0 détermine si les registres seront autorisés. SG1 détermine si le PALCE16V8 émulera une famille PAL16R8 ou un périphérique de la famille PAL10H8. Dans chaque macrocellule, SLO<sub>x</sub>, en conjonction avec SG1, sélectionne la configuration de la macrocellule, et SL1<sub>x</sub> définit la sortie comme active basse ou active haute pour la macrocellule individuelle. Les bits de configuration fonctionnent

en agissant comme des entrées de commande pour les multiplexeurs de la macrocellule. Il existe quatre multiplexeurs : une entrée de terme de produit, une sélection d'activation, une sélection de sortie et un multiplexeur de sélection de rétroaction. SG1 et SLOx sont les signaux de commande des quatre multiplexeurs. Dans MC<sub>0</sub> et MC<sub>7</sub>, SGO remplace SG1 sur le multiplexeur de rétroaction. Cela permet à CLK d'être la broche adjacente pour MC7 et OE la broche adjacente pour MC<sub>0</sub>.

#### **Configuration de sortie enregistrée**

Les paramètres du bit de contrôle sont SGO = 0, SG1 = 1 et SLOx = 0. Il n'y a qu'une seule configuration enregistrée. Les huit termes du produit sont disponibles en tant qu'entrées de la porte OU. La polarité des données est déterminée par SL1x. La bascule est chargée sur la transition LOW-to-HIGH de CLK. Le chemin de rétroaction provient de Q sur le registre. Le tampon de sortie est activé par OE. Configurations combinatoires Le PALCE16V8 a trois configurations de sortie combinatoires : sortie dédiée dans un périphérique non enregistré, E / S dans un périphérique non enregistré et E / S dans un périphérique enregistré appareil.

#### **Sortie dédiée dans un périphérique non enregistré**

Les paramètres du bit de contrôle sont SGO = 1, SG1 = 0 et SLOx = 0. Les huit conditions de produit sont disponibles pour la porte OU. Bien que la macrocellule soit une sortie dédiée, la rétroaction est utilisée, à l'exception des broches 15 et 16. Les broches 15 et 16 n'utilisent pas de rétroaction dans ce mode. Comme CLK et OE ne sont pas utilisés dans un périphérique non enregistré, les broches 1 et 11 sont disponibles en tant que signaux d'entrée. La broche 1 utilisera le chemin de rétroaction de MC7 et la broche 11 utilisera le chemin de rétroaction de MC<sub>0</sub>.

#### **E / S combinatoires dans un Périphérique**

Les paramètres du bit de contrôle sont SGO = 1, SG1 = 1 et SLOC = 1. Seules sept conditions de produit sont disponibles pour la porte OU. Le huitième terme de produit est utilisé pour activer le tampon de sortie. Le signal sur la broche d'E / S est renvoyé au réseau ET via le multiplexeur de rétroaction. Cela permet à la broche d'être utilisée comme entrée. Comme CLK et OE ne sont pas utilisés dans un appareil non enregistré, les broches 1 et 11 sont disponibles en tant qu'entrées. La broche 1 utilisera le chemin de rétroaction de MC<sub>0</sub>. Et la broche 11 utilisera le chemin de rétroaction de MC<sub>0</sub>.

#### **E / S combinatoires dans un périphérique enregistré**

Les paramètres de bit de contrôle sont SGO = 0, SG1 = 1 et SLOx = 1. Seules sept conditions de produit sont disponibles pour la porte OU. Le huitième terme de produit est utilisé comme validation de sortie. Le signal de retour est l'E / S correspondante signal.

#### **Configuration d'entrée dédiée**

Les paramètres du bit de contrôle sont  $SG0 = 1$ ,  $SG1 = 0$  et  $SLOx = 1$ . Le tampon de sortie est désactivé. Sauf pour  $MC_0$  et  $MC_7$ , le signal de retour est une E / S adjacente. Pour  $MC_0$  et  $MC_7$ , les signaux de retour sont les broches 1 et 11. Ces configurations sont résumées dans le tableau 2 et illustrées dans la figure 28.

### Polarité de sortie programmable

La polarité de chaque macrocellule peut être active-elevée ou active-basse, soit pour correspondre aux besoins du signal de sortie, soit pour réduire les conditions du produit. La polarité programmable permet d'écrire les expressions booléennes dans leur format le plus compact forme (vraie ou inversée), et la sortie peut toujours être de la polarité souhaitée. Il peut également enregistrer "DeMorganizing" efforts. La sélection se fait par un bit programmable  $SL1x$  qui commande une porte OU exclusif à la sortie de la logique ET / OU. La sortie est active haut si  $SL1x$  est 1 et active bas si  $SL1x$  est 0.

Le PAL versatile (polyvalent), dont le membre le plus connu est le 22V10, présente une évolution des PAL vers les circuits logiques programmables de plus haut niveau. Mais ils utilisent une structure de cellule de sortie qui s'apparente à un EPLD. D'après la figure suivante, on remarque que la cellule de sortie dispose d'une bascule D pré-positionnable associée à deux multiplexeurs programmables. Les connexions  $S0$  et  $S1$  sont réalisées grâce à des fusibles internes.

Le bloc de sortie des PAL versatiles permet de configurer (par programmation) le mode d'utilisation de la broche de sortie.

Figure 26. Macro cellule de PALCE16V8

Figure 27. PALCE16V8

Cette sortie peut adopter plusieurs configurations (d'où le terme polyvalent), le 22V10 pouvant donc être utilisé à la place de tous les PAL bipolaires classiques :

Les structures de sorties dite versatile proposent quatre configurations possibles suivant les valeurs de S0 et S1.

Ce qui donne :

| <b>SG0</b> | <b>SG1</b> | <b>SL0x</b> | <b>configuration</b>          |

|------------|------------|-------------|-------------------------------|

| 0          | 1          | 0           | sortie à registre             |

| 0          | 1          | 1           | Registre et combinatoire E/S. |

| 1          | 0          | 0           | sortie combinatoire           |

| 1          | 0          | 1           | Entrée combinatoire           |

| 1          | 1          | 1           | combinatoire E/S.             |

Table 2. Différentes configurations

Figure 28. Différentes configurations de la macrocellule

Les premiers PAL pouvaient être assez facilement programmés à la main. Toutefois, la réalisation de fonctions complexes est devenue rapidement inextricable. Des logiciels de développement sont donc apparus afin de faciliter ce travail.

Tous les PAL disposent d'un fusible ou bit de sécurité. Ce fusible, une fois claqué, interdit la relecture d'un composant déjà programmé. En effet, il arrive que des entreprises indélicates soient tentées de copier les PAL développés par leurs concurrents.

Un des inconvénients des circuits bipolaires à fusibles, est qu'ils ne peuvent pas être testés à la sortie de l'usine. Pour tester leur fonctionnement, il faudrait en effet claquer les fusibles, ce qui interdirait toute programmation ultérieure. A l'origine, les premiers PAL étaient bipolaires puisqu'ils utilisaient la même technologie que les PROM bipolaires à fusibles. Il existe maintenant des PAL en technologie CMOS (appelés GAL (Generic Array Logic) par certains fabricants), programmables et effaçables électriquement, utilisant la même technologie que les mémoires EEPROM. Comme ils sont en technologie CMOS, ils consomment beaucoup moins, en statique, que les PAL bipolaires de complexité équivalente.

#### 1.8.4.4 Les références des PAL

Exemple :

PAL CE 16 V 8 H -5 P C /5

**PAL** : Type de famille (PAL=Programmable Array Logic)

**CE** : Technologie (CE= CMOS Effaçable Electriquement)

**16** : Nombre d'entrées

**V** : type de sortie (V : PAL Versatile

H : PAL combinatoire active au niveau Haut

L : PAL combinatoire active au niveau Bas

C : Sortie Complémentaire

R : Sortie à registre

X : Sortie OU exclusif avec registre)

**8** : Nombre de sorties

**H** : Puissance (H=1/2 W 90-125mA)

Q= 1/4 W 55 mA)

**-5** : La vitesse (-5 : 5 ns

-7 : 7.5 ns

-10 : 10 ns

-15 : 15 ns

-20 : 20 ns

-25 : 25 ns)

**P** : Type de boitier (P : 20 broches plastique DIP (PD 020)

J : 20 broches support plombée en plastique

S : 20 broches ensemble en plastique type Gull-Wing (So 020))

- C : Conditions d'utilisations (C : commerciale (0°C à +75°C)

I : industriel (-40°C à +85°C))

/5 : Désignation de programmation (blanc : Algorithme initial

/4 : Première révision

/5 : Deuxième révision)

### 1.8.5 GAL

Au fur et à mesure que la popularité du PAL augmentait, des fonctionnalités supplémentaires ont été mises en œuvre pour prendre en charge des conceptions plus sophistiquées. L'une des améliorations les plus significatives a été l'ajout d'une logique de sortie macrocellule (OLMC). Une OLMC a fourni une bascule D et un multiplexeur sélectionnable afin que la sortie du circuit SOP du PAL puisse être utilisée soit comme sortie système soit comme entrée d'une bascule D. Cela a permis la mise en œuvre de la logique séquentielle et des machines à états finis. La OLMC pourrait également être utilisée pour acheminer la broche d'E/S vers le PAL afin d'augmenter le nombre d'entrées possibles dans les expressions SOP. Enfin, la OLMC a fourni un multiplexeur pour permettre la rétroaction de la sortie PAL ou de la sortie de la bascule D. Cette architecture a été nommée une logique de tableau générique (GAL) pour distinguer ses fonctionnalités d'un PAL standard.

GAL signifie Generic Array Logic ou encore réseau logique le nom de GAL a été déposé par LATTICE SEMICONDUCTOR. Leur fonctionnement est identique aux PAL CMOS.

- Les GAL sont des PAL à technologie CMOS, sont programmables et effaçables électriquement.

- On retrouve les mêmes références qu'en PAL.

#### **Protection contre la duplication :**

Les GAL sont dotés d'un bit de sécurité (empêchant la lecture du contenu du circuit). Ils sont constitué de 8 octets appelés signature qui contiennent des infos sur le produits.

#### **Avantage des GALs / aux PALs :**

L'inconvénient majeur des PALs est qu'ils ne sont programmables qu'une seule fois. LATTICE a donc pensé, il y a un peu plus de 10 ans, à remplacer les fusibles irréversibles des PALs par des transistors MOS FET pouvant être régénérés. Ceci a donc donné naissance aux GALs que l'on pourrait traduire par « Réseau logique Générique ». Ces circuits peuvent donc être reprogrammés à volonté sans pour autant avoir une durée de

vie restreinte. On peut aussi noter que dans leur structure interne les GALs sont constitués de transistor CMOS alors que les PALs classiques sont constitués de transistors bipolaires. La consommation des GALs est donc beaucoup plus faible. Depuis d'autres constructeurs fabriquent ce type de produit en les appellants « PAL CMOS » (PAL CE). Par soucis de remplacer les PALs, LATTICE a équipé la plupart de ses GALs de macrocellules programmables permettant d'émuler n'importe quel PAL. Ces structures de sortie sont donc du type « Versatile » (V).

#### 1.8.6 Hard Array Logic (HAL)

Pour les conceptions matures, les PAL et les GAL pourraient être implémentés en tant que dispositif logique à matrice dure (HAL). Un HAL était une version d'un PAL ou GAL qui avait les connexions de plan ET implémentées pendant la fabrication au lieu de souffler des fusibles. Cette architecture était plus efficace pour les applications à volume élevé car elle éliminait l'étape de programmation post-fabrication et le dispositif n'avait pas besoin de contenir les circuits de programmation.

En 1983, Altera Inc. a été fondée en tant qu'entreprise de dispositifs logiques programmables. En 1984, Altera a sorti sa première version d'un PAL avec une caractéristique unique qu'il pouvait être programmé et effacé plusieurs fois en utilisant un programmeur et une source de lumière UV similaire à une EEPROM.

#### 1.8.7 Les EPLD :

Les EPLD (Erasable Programmable logic Device) sont des circuits programmables électriquement et effaçables, et qui sont aux P.A.L. ce que sont les U.V.P.R.O.M. Aux P.R.O.M. Les E.P.L.D. peuvent être effacés par U.V. ou électriquement. Ils sont encore appelés P.A.L. CMOS. Historiquement, les premiers EPLD étaient des GAL effaçables aux U.V. Il existe maintenant des EPLD effaçables électriquement.

Ces circuits, développés en premier par la firme ALTERA, sont arrivés sur le marché en 1985. Les EPLD sont une évolution importante des PAL CMOS. Ils sont basés sur le même principe pour la réalisation des fonctions logiques de base. Les procédés physiques d'intégration permis par les EPLD sont nettement plus importants que ceux autorisés par les PAL CMOS. Ces circuits ont une capacité en nombre de portes et en possibilités de configuration est supérieure à celle des GAL.

En effet, les plus gros EPLD actuellement commercialisés intègrent jusqu'à 24000 portes logiques dont 12000 sont réellement accessibles à l'utilisateur. On peut ainsi loger dans un seul boîtier, l'équivalent d'un schéma logique utilisant jusqu'à 50 à 100 PAL classiques.

- Densité d'intégration supérieure aux PAL.

- Fonctionner à une vitesse au moins égale aux PAL bipolaire.

Description fonctionnelle :

EPLD de la famille MAX :

- ❖ Logic Array broches(LABs)

- ❖ Macro cellules

- ❖ Ex panseur

- ❖ Réseaux d'Interconnections Programmables (PIA)

- ❖ I/O control blocks

Comme les PAL CMOS, les EPLD font appel à la notion de macrocellule qui permet, par programmation, de réaliser de nombreuses fonctions logiques combinatoires ou séquentielles.

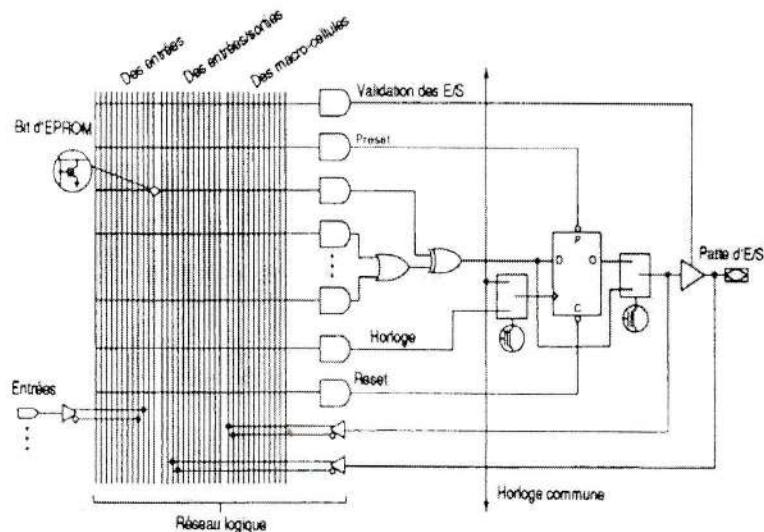

Le schéma type de la macrocellule de base d'un EPLD est présenté ci-dessous. On remarque que le réseau logique est composé de 3 sous-ensembles :

- le réseau des signaux d'entrées provenant des broches d'entrées du circuit,

- le réseau des signaux des broches d'entrées/sorties du circuit,

- le réseau des signaux provenant des autres macrocellules.

Figure 29. Macrocellule d'un EPLD

Outre la logique combinatoire, la macrocellule possède une bascule configurable (bascule D, T, RS ou JK). Cette bascule peut être désactivée par programmation d'un multiplexeur. Le signal d'horloge peut être commun à toutes les macrocellules, ou bien provenir d'une autre macrocellule via le réseau logique.

La partie nommée OLMC (OUTPUT LOGIC MACROCELL) est versatile, ce qui veut dire qu'il est possible par programmation de choisir entre une configuration de sortie combinatoire ou séquentielle.

La figure ci-dessous montre la structure et la table de fonctionnement d'une OLMC :

- Le multiplexeur 4 vers 1 permet de mettre en circuit ou non la bascule D, en inversant ou non les signaux.

- Le multiplexeur 2 vers 1 permet de réinjecter soit la sortie, soit l'entrée du buffer de sortie vers la matrice.

Figure 30. Macro cellule configurable

Quel que soit la famille d'EPLD, la fonctionnalité de la macrocellule ne change guère. En revanche, plus la taille des circuits augmentent, plus les possibilités d'interconnexions et le nombre de macrocellules augmentent. On voit ci-dessous la structure d'un EPLD de la famille MAX 5000 d'ALTERA.

Il existe plusieurs types d'EPLD en technologie CMOS :

- Les circuits programmables électriquement et non effaçables. Ce sont les EPLD de type OTP (One Time Programmable).

- Les circuits programmables électriquement et effaçables aux UV.

- Les circuits programmables électriquement et effaçables électriquement dans un programmeur.

- Les circuits programmables électriquement et effaçables électriquement sur la carte (ISP : In Situ Programmable), utilisant une tension unique de 5 V.

Les plus rapides des EPLD ont des temps de propagation (entrée vers sortie sans registre) de l'ordre de 12 ns. En revanche, comme ils sont en technologie CMOS, leur consommation croît avec l'augmentation de la fréquence de fonctionnement. Le taux d'utilisation des ressources d'un EPLD dépasse rarement 80 %. Avec les EPLD, il est possible de prédire la fréquence de travail maximale d'une fonction logique, avant son implémentation. On rencontre parfois le terme CPLD (Complex Programmable Logic Device). Ce terme est généralement utilisé pour désigner des EPLD ayant un fort taux d'intégration.

#### 1.8.8 LES CPLD :

Alors que de la demande de dispositifs programmables augmenté de plus en plus.

L'architecture du PAL n'a pas pu évoluer efficacement pour un certain nombre de raisons :

- premièrement, à mesure que la taille des circuits de logique combinatoire augmentait, le PAL a rencontré des problèmes de fan-in dans son plan ET.

- deuxièmement, pour chaque entrée ajoutée au PAL, la quantité des circuits nécessaires sur la puce a augmenté géométriquement en raison de la nécessité d'une connexion à chaque porte ET en plus de la zone associée à la CLOSM supplémentaire.

Cela a conduit à une nouvelle architecture PLD dans laquelle l'interconnexion sur puce a été partitionnée sur plusieurs PAL sur une seule puce. Ce partitionnement signifiait que toutes les entrées de l'appareil ne pouvaient pas être utilisées par chaque PAL, de sorte que la complexité de la conception augmentait, cependant, les ressources programmables supplémentaires ont compensé cet inconvénient, et cette architecture a été largement adoptée. Cette nouvelle architecture a été appelée un dispositif logique programmable complexe (CPLD).

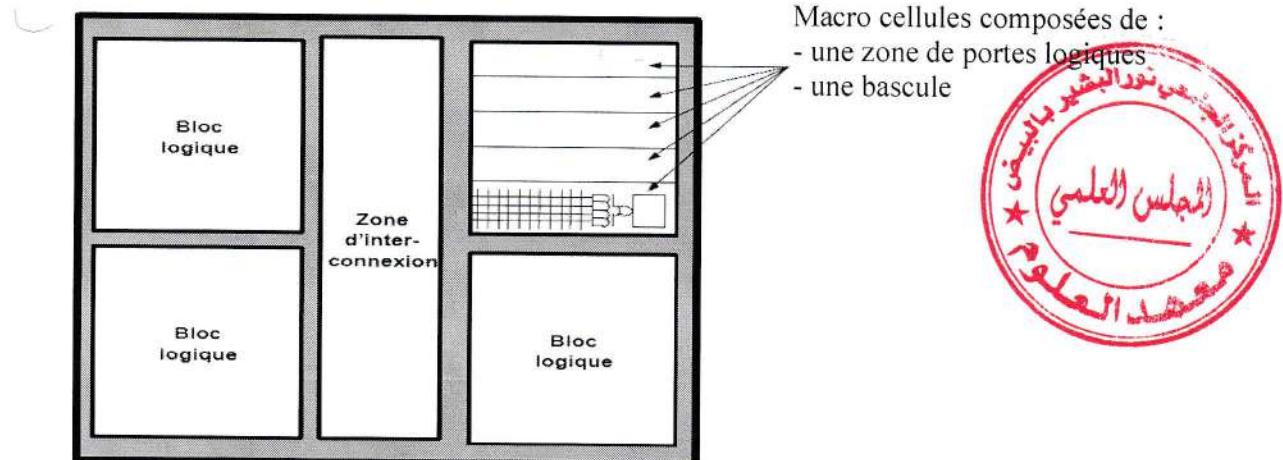

CPLD signifie Complex Programmable Logic Device ces circuits sont composés de plusieurs PALs élémentaires reliés entre eux par une zone d'interconnexion. Leurs architectures sont basées sur celles des PALs. Grâce à cette architecture, ils permettent d'atteindre des vitesses de fonctionnement élevées (plusieurs centaines de MHz).

Ces circuits ont une capacité en nombre de portes et en possibilités de configuration très supérieure à celle des PALs. Le nombre de portes peut varier entre 100 et 100 000 portes logiques et entre 16 et 1000 bascules.

#### 1.8.8.1 Structure générale d'un CPLD :

Figure 31. Macrocellule d'un CPLD

#### 1.8.9 Les FPGA :

Pour répondre au besoin de ressources encore plus programmables, une nouvelle architecture a été développée par Xilinx Inc. en 1985. Cette nouvelle architecture a été appelée un réseau de portes programmables sur site (FPGA). Un FPGA se compose d'un tableau de blocs logiques programmables (ou d'éléments logiques) et d'un réseau d'interconnexion programmable qui peut être utilisé pour connecter n'importe quel élément logique à n'importe quel autre élément logique. Chaque circuit logique contenu dans un bloc pour mettre en œuvre des circuits logiques combinatoires arbitraires en plus d'une bascule D et d'un multiplexeur pour la direction du signal. Cette architecture a mis en œuvre efficacement une CLOSM dans chaque bloc, offrant ainsi une flexibilité ultime et fournissant beaucoup plus de ressources pour la logique séquentielle. Aujourd'hui, les FPGA sont les dispositifs logiques programmables les plus couramment utilisés, Altera Inc. et Xilinx Inc. étant les deux plus grands fabricants. La Figure 32 montre l'architecture générique d'un FPGA.

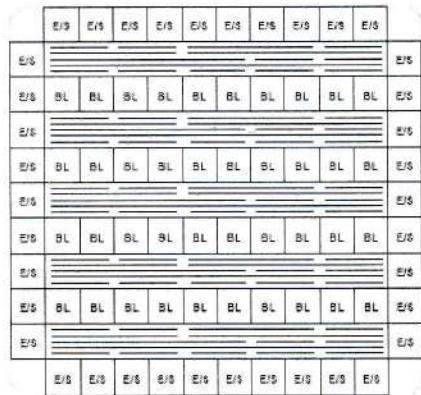

Figure 32. Cellule de base d'un FPGA

Les cellules de base d'un FPGA sont disposées en rangées et en colonnes. Des lignes d'interconnexions programmables traversent le circuit, horizontalement et verticalement, entre les diverses cellules. Ces lignes d'interconnexions permettent de relier les cellules entre elles, et avec les plots d'entrées/sorties. Les connexions programmables sur ces lignes sont réalisées par des transistors MOS dont l'état est contrôlé par des cellules mémoires SRAM. Ainsi, toute la configuration d'un FPGA est contenue dans des cellules SRAM. Contrairement aux EPLD, on ne peut pas prédire la fréquence de travail maximale d'une fonction logique, avant son implémentation. En effet, cela dépend fortement du résultat de l'étape de placement routage.

Les FPGAs à la différence des CPLDs sont assimilables à des A.S.I.C. (Application Specific Integrated Circuit) programmables par l'utilisateur. La puissance de ces circuits est telle qu'ils peuvent être composés de plusieurs milliers voire millions de portes logiques et de bascules. Les dernières générations de FPGA intègrent même de la mémoire vive (RAM). Les deux plus grands constructeurs de FPGA sont XILINX et ALTERA. Ils sont composés de blocs logiques élémentaires (plusieurs milliers de portes) qui peuvent être interconnectés. De plus en plus les capacités des CPLDs et des FPGAs se rapprochent. Le principal critère de choix entre les deux familles est la vitesse de fonctionnement. En effet les CPLDs acceptent des fréquences de fonctionnement beaucoup plus élevées que les FPGAs. Chaque bloc configurable est constitué de réseau de portes logiques ou des fonctions logiques complexes (compteur, multiplexeur etc...).

Figure 33. Structure d'un FPGA de type Xilinx.

Par une simple programmation électrique (d'une mémoire SRAM) on peut :

- configurer un bloc logique ou plusieurs

- interconnecter entre eux les blocs grâce à une matrice de connexion

On peut aussi électriquement déprogrammer ce que l'on avait programmé.

#### Comparaison entre CPLD et FPGA :

|      | Avantages                              | Inconvénients                            |

|------|----------------------------------------|------------------------------------------|

| CPLD | Non volatile                           |                                          |

|      | Compteur et machines d'états rapides   | Les ressources de routage sont faibles   |

|      | Logique combinatoire ou de contrôle    | Fonction réclamant peu de routage        |

|      | Les temps d'arrives sont déterministes |                                          |

| FPGA | Architecture micro programmée, DSP     | Les temps d'arrives dépendent du routage |

|      | Système séquentielle                   | Reconfiguration par SRAM                 |

|      | Densité d'intégration élevée           | Nécessite une PROM (non volatile)        |

Table 3. Tableau comparative entre CPLD et FPGA

## **Chapitre 2 : Les technologies des éléments programmables**

---

## 2.1 Les Technologies d'interconnexion :

Premier critère de choix d'un circuit programmable, la technologie utilisée pour matérialiser les interconnexions détermine les aspects électriques de la programmation : maintien (ou non) de la fonction programmée en l'absence d'alimentation, possibilité (ou non) de modifier la fonction programmée, nécessité (ou non) d'utiliser un appareil spécial (un programmeur).

L'un des éléments clé des circuits étudiés est la connexion programmable. Le choix d'une technologie dépendra essentiellement :

- la densité d'intégration

- la rapidité de fonctionnement une fois le composant programmé ; fonction de la résistance à l'état passant et des capacités parasites

- la facilité de mise en œuvre (programmation sur site, reprogrammation etc.)

- la possibilité de maintien de l'information

### Connexions programmable une seul fois (OTP : One Time Programming)

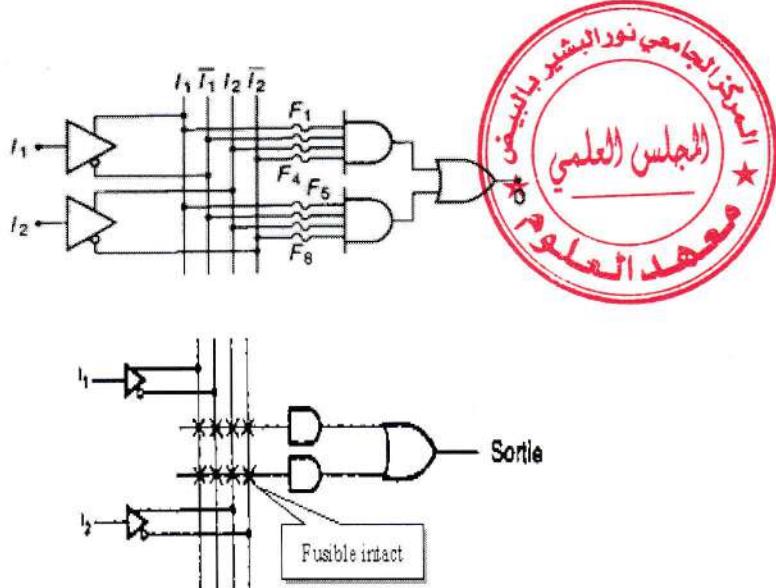

#### 2.1.1 Les cellules à fusible :

Première méthode employée, la connexion par fusibles, est en voie de disparition. On ne la rencontre plus que dans quelques circuits de faible densité, de conception ancienne. Leur principe consistait à détruire un fusible conducteur par passage d'un courant fourni par une tension supérieure à alimentation (12 à 25V).

Figure 34. Cellule élémentaire d'un PLD à fusibles

La figure ci-dessus illustre le principe ; toutes les connexions sont établies à la fabrication.

La connexion est supprimée par claquage du fusible, obtenu par l'application d'une tension (de 12 à 25 V)

Cette technologie maintenant abandonnée pour des raisons de manque de fiabilité. Le fait de griller les fusibles provoque des perturbations qui peuvent affecter le reste du circuit. De plus, cette programmation est irréversible et ne permet pas donc la reprogrammation.

### 2.1.2 Les Cellules à anti fusible :

En appliquant une tension importante (6 v pendant 1 ms) à un isolant entre deux zones de semi-conducteur fortement dopées, ce dernier diffuse dans l'isolant et le rend conducteur. Chaque cellule occupe environ  $1.8 \mu\text{m}^2$  ( $700 \mu\text{m}^2$  pour un fusible) ; cette technologie très en vogue permet une haute densité d'intégration.

Le principe est, à l'échelle microscopique, celui de la soudure électrique par points. Un point d'interconnexion est réalisé au croisement de deux pistes conductrices (métal ou semi-conducteur selon les procédés de fabrication), séparées par un isolant de faible épaisseur. Une surtension appliquée entre les deux pistes provoque un perçage définitif du diélectrique, ce qui établit la connexion.

### 2.1.3 Les cellules anti-fusibles à diélectrique

Un antifusable est un élément programmable qui à l'inverse des fusibles n'est passant qu'après programmation. La connexion s'effectue en détruisant un diélectrique

Disposition verticale → gain en surface élaboré par Actel en 1986.

Figure 35. Cellule antifusable à diélectrique

PLICE : Programmable Low Impedance Circuit Element sandwich conducteur/isolant/conducteur surface de la cellule =  $1,8 \mu\text{m}^2$

### 2.1.4 Les cellules anti-fusibles en silicium amorphe

Technologie introduite par Cypress même fonction que la précédente avec une résistance plus faible à l'état passant ce qui réduit les délais de propagation à travers les interconnexions.

### Cellules reprogrammables :

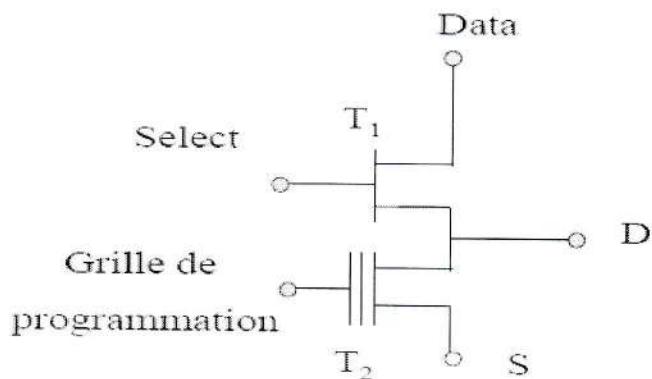

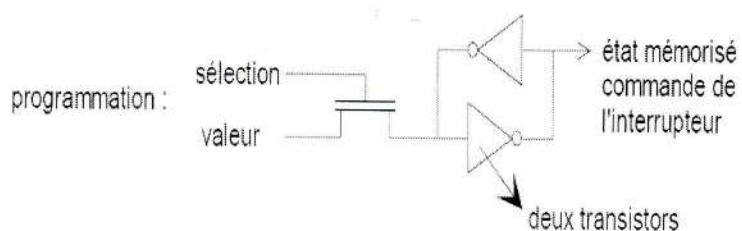

### 2.1.5 Les cellules à transistors MOS à grille flottante et EPROM

L'apparition du transistor MOS à grille flottante a permis de rendre le composant bloqué ou passant sans application permanente d'une tension de commande. Le principe consiste à piéger ou non (à l'aide d'une tension supérieur à la tension habituelle d'alimentation) des électrons dans la grille.

Programmation : piéger des électrons dans la grille flottante qui s'opposent à la conduction dans le canal ; le transistor est alors équivalent à un interrupteur ouvert. Lorsque le transistor n'est pas programmé, la grille flottante ne contient aucun électron, le canal est conducteur et le transistor est équivalent à un interrupteur fermé. L'extraction éventuelle des électrons piégés permet le retour à l'état initial.

Lorsque le transistor n'est pas programmé, la grille flottante ne contient aucun électron, le canal est conducteur et le transistor est équivalent à un interrupteur fermé.

Le dépôt d'une charge électrique sur la grille isolée d'un transistor fait appel à un phénomène connu sous le nom *d'effet tunnel* : un isolant très mince (une cinquantaine d'angstroms,  $1 \text{ \AA} = 10^{-10} \text{ m}$ ) soumis à une différence de potentiel suffisamment grande (une dizaine de volts, supérieure aux 3,3 ou 5 volts des alimentations classiques) est parcouru par un courant de faible valeur, qui permet de déposer une charge électrique sur une électrode normalement isolée. Ce phénomène, réversible, permet de programmer et d'effacer une mémoire. Plusieurs technologies EPROM sont en concurrence.

La figure suivante montre la structure du PLD élémentaire précédent, dans lequel les fusibles sont remplacés par des transistors à grille isolée (technologie FLASH).

Figure 36. PLD simple à MOS

Figure 37. Caractéristique  $I_D=f(V_{GS})$  pour effacement et programmation

### 2.1.6 Les Cellules UV EPROM :

Les connexions sont réinitialisable par une exposition à un rayonnement ultra-violet d'une vingtaine de minutes (d'une durée d'environ 20 minutes), permet d'annuler la charge stockée dans la grille flottante. Effacement non sélectif reproductible plus d'un millier de fois.

### 2.1.7 Les Cellules EEPROM : (Electrically EPROM)

L'effacement et la programmation se font cette fois électriquement avec une tension de 12v et peuvent être ( $75 \text{ à } 100 \mu\text{m}^2$  en CMOS 0.6  $\mu\text{m}$ ) et réduit la densité d'intégration possible. D'autre part le nombre de cycles de programmation est limite à un nombre de 100 (en CMOS 0.6  $\mu\text{m}$ ) à 10 000 (en CMOS 0.8  $\mu\text{m}$ ) à cause de la dégradation des isolants. La programmation ou l'effacement d'une cellule dure quelques ms).

Figure 38. Cellule EEPROM

### 2.1.8 Les Cellules Flash EEPROM :

L'utilisation de deux transistors par cellule uniquement (5 pour l'EEPROM) et une structure verticale permettent une densité intégration importante ( $25 \mu\text{m}^2$  par cellule en CMOS 0.6  $\mu\text{m}$ ) trois à quatre fois plus importante que l'EEPROM, mais quand même 10

fois moins que la technologie à antifusible. Le nombre de cycle d'écriture ( $10^4$  à  $10^6$ ) est également plus grand que pour l'EEPROM car l'épaisseur de l'isolant est plus importante. Par contre la simplicité de la cellule élémentaire n'autorise pas une reprogrammation sélective (éventuellement par secteur).

La tension de programmation et d'effacement est de 12v, avec un temps de programmation de quelques dizaines de  $\mu s$  pour un temps d'effacement de quelques ms. Un des inconvénients des cellules flash et EEPROM de nécessiter une alimentation supplémentaire pour la programmation et effacement est pallié les constructeurs en intégrant dans le circuit un système à pompe de charge fournissant cette alimentation. Le composant peut alors être programmé directement sur la carte ou il est utilisé. On parle alors de composant ISP (in situ programmation ou encore suivant les sources, in system programmation).

Figure 39. Cellule Flash EEPROM

Programmation 1000 fois plus rapide que l'effacement.

Plusieurs cellules sont programmées simultanément.

Nombre de cycles de programmation supérieur à 10000.

### 2.1.9 Les technologies à RAM statique -SRAM

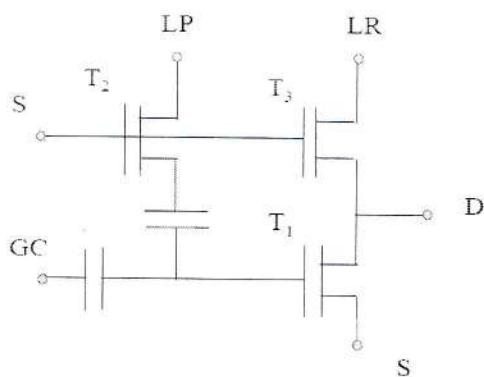

#### 2.1.10 Les Cellules SRAM à transistors MOS classique :

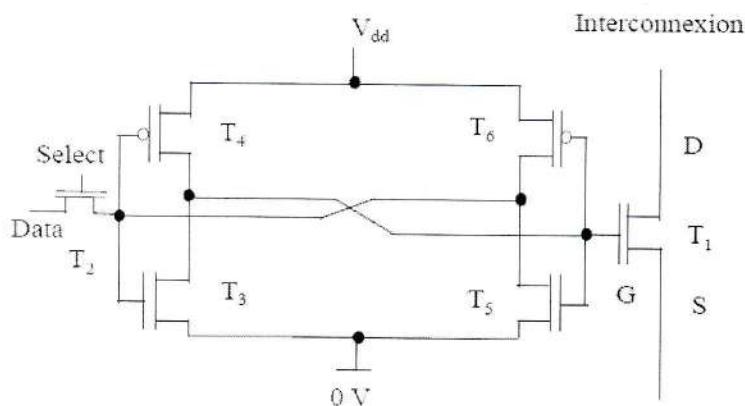

Ce principe est classiquement choisi pour le FPGA.

Dans les circuits précédents, la programmation de l'état des interrupteurs, conservée en l'absence de tension d'alimentation, fait appel à un mode de fonctionnement électrique particulier. Dans les technologies à mémoire statique (SRAM), l'état de chaque interrupteur est commandé par une cellule mémoire classique à quatre transistors (plus

un transistor de programmation), dont le schéma de principe est celui de la figure suivante.

*Figure 40. Cellule SRAM*